# A Novel Voltage-Mode Lut Using Clock Boosting Technique in Standard CMOS

#### Sathyavathin S1\* and Mr Ilanthendral J2

<sup>1</sup>Final Year M.E (VLSI design), Department of ECE, Adhiparasakthi Engineering College, Melmaruvathur, TN, India <sup>2</sup>Assistant Professor, ECE Department, Adhiparasakthi Engineering College, Melmaruvathur, TN, India

#### Abstract

In a VLSI circuit, interconnection plays the dominant role in every part of the circuit nearly 70 percent of the area depends on interconnection, 20 percent of area depends on insulation, and remaining 10 percent to devices. The binary logic is limited due to interconnect which occupies large area on a VLSI chip. In this work, the designs of quaternary-valued logic circuits have been explored over multi-valued logic due to the following reasoning. An approach to mitigate the impact of interconnections is to use multiple-valued logic (MVL), hence, more information can be carried in each wire, reducing the routing network. Therefore, a single wire carrying a signal with N logic levels can replace log N having base 2 wires carrying binary signals. Reducing the routing leads to a direct reduction of the line capacitance and the overall circuit area. Therefore, this results in increasing the maximum operation frequency and also reducing the power consumption. The most important characteristics of this method is a voltage-mode structure. Voltage mode structure has the advantages like reduced power consumption implemented in a standard CMOS technology. Our new method overcomes conventional techniques with simple and efficient CMOS structures.

**Keywords:** Multiple-value logic; Quaternary logics; Look- up tables; FPGAs; Standard CMOS technology

#### Introduction

Central processing unit power dissipation or CPU power dissipation is the process in which central processing units (CPUs) consume electrical energy, and dissipate this energy both by the action of the switching devices contained in the CPU and by the energy lost in the form of heat due to the impedance of the electronic circuits. Mainly occurs due leakage current and static power dissipation and has formula [1]

$$P_d \propto \mathbf{CV}_{\mathbf{2dd}} \tag{1}$$

Therefore by reducing the capacitance value we can able to reduce the dissipation. One of the important advantage of quaternary logic is that has the reduced noise margin when compared to the conventional binary logic. More over if we use the current mode we have to face the problem for the fabrication process and have the high power consumptions [2].

#### **Binary and quaternary Look-Up tables**

In General Look-Up Tables (LUT) are basically memories, which implement a logic Function according to their configuration. Configuration values C=(c0....ci, ck-1); are initially stored in the look-up table structure, and once inputs are applied to it, the logic value in the addressed position is assigned to the output.

The capacity of a LUT

$$|C|$$

is given by

$$|\mathbf{C}| = \mathbf{n}_{\mathbf{x}} \mathbf{b}_{\mathbf{k}} \tag{2}$$

Where n denotes the number of outputs, k denotes the number of inputs and b for the number of logic values. For example, a 4-input binary look-up table with one output is able to store  $1 \times 24=16$  Boolean values.

A binary function implemented by a Binary Look-Up Table (BLUT) is defined as f:  $Bk \rightarrow B$ , over a set of variables X=(x0,...xi,...; xK-1), where each variable xi represents a Boolean value. The total number of different functions |F| that can be implemented in a BLUT

with k input variables is given by

$$\mathbf{F} = \mathbf{b}_{|\mathbf{C}|} \tag{3}$$

Where b=|B| (b=2 in the binary case). For example, a look-up table with 4 inputs (k=4) can implement one of |F|=65,536 different functions. Quaternary functions are basically generalizations from binary functions. This function implemented by a quaternary look-up table (QLUT) is defined as g: Qk  $\rightarrow$  Q, over a set of quaternary variables Y=(y0,.... yi ....... yk-1), where the values of a variable yi, as the values of the function g(Y), can be in Q= {0,1,2,3}. As in the binary case, the number of possible function in QLUTs is given by (2), where b=4. In this case, the number of functions that can be represented is everywhere 4.3×109 for aQLUT with only two quaternary inputs (k=2), which is much larger than for the BLUT [3].

The quaternary variable y is capable of representing twice as much information as a binary variable x, we note that the cardinality of  $|Q|=2 \times |B|$  in our experiments. In other words, two binary variables with the same inputs can be grouped in order to represent a quaternary variable. Such procedure is used mainly for reducing both the total number of connections and the number of gates.

#### Quaternary logic and reference voltages levels

This design was implemented using a standard CMOS technology, a single supply voltage and a clock boosting technique to incorporate a 16 to 1 multiplexer and a dual quaternary decoder. One of the most

\*Corresponding author: Sathyavathin S, Final Year M.E (VLSI design), Department of ECE, Adhiparasakthi Engineering College, Melmaruvathur, Tamilnadu, India, E-mail: nssathyavathi@gmail.com

Received December 08, 2014; Accepted January 22, 2014; Published February 10, 2015

**Citation:** Sathyavathin S, Ilanthendral J (2015) A Novel Voltage -Mode Lut Using Clock Boosting Technique in Standard CMOS. J Electr Electron Syst 4: 139. doi:10.4172/2332-0796.1000139

**Copyright:** © 2015 Sathyavathin S, et al. This is an open-access article distributed under the terms of the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original author and source are credited.

important feature that was taken into account was the area usage since that, in order to perform more complex functions, this circuit needs to be replicated a millions of times in the FPGA [4].

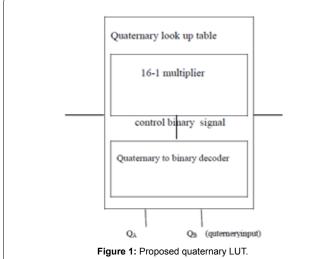

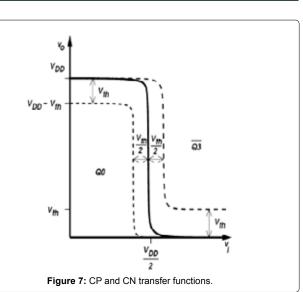

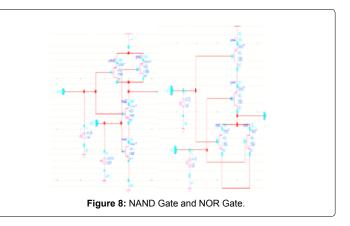

The circuit depicted in the table below has two quaternary inputs, QA and QB, which are then computed by the dual quaternary decoder into the QLUT's binary control signals, B00-B33. The multiplexer 16to-1 consists of sixteen NMOS switches enhanced with a clock boosting technique. When one of the control signals is high, the corresponding QLUT's line- switch- is activated connecting the corresponding QLUT's quaternary input to the output. The four voltage levels are represented in Table 1.

A quaternary variable can assume four different logic levels. Assuming a rail-to-rail voltage range and equal noise margins for the four logic levels, three different reference voltage values are required, 1/6VDD, 3/6VDD, and 5/6VDD, to determine a quaternary value.

| Value | Voltage value [v] |  |  |

|-------|-------------------|--|--|

| 0     | 0                 |  |  |

| 1     | 0.404             |  |  |

| 2     | 0.707             |  |  |

| 3     | 1.2               |  |  |

Table 1: The four voltage levels.

| Figure 1: Proposed quaternary LUT. |   |   |   |   |         |   |   |  |

|------------------------------------|---|---|---|---|---------|---|---|--|

|                                    |   |   |   |   |         |   |   |  |

| Decimal                            | 8 | 4 | 2 | 1 | Decimal | 4 | 1 |  |

| 0                                  | 0 | 0 | 0 | 1 | 0       | 0 | 0 |  |

| 1                                  | 0 | 0 | 1 | 0 | 1       | 0 | 1 |  |

| 2                                  | 0 | 0 | 1 | 1 | 2       | 0 | 0 |  |

| 3                                  | 0 | 1 | 0 | 0 | 3       | 0 | 1 |  |

| 4                                  | 0 | 1 | 0 | 0 | 4       | 1 | 0 |  |

| 5                                  | 0 | 1 | 0 | 1 | 5       | 1 | 1 |  |

| 6                                  | 0 | 1 | 1 | 0 | 6       | 1 | 0 |  |

| 7                                  | 0 | 1 | 1 | 1 | 7       | 1 | 1 |  |

| 8                                  | 1 | 0 | 0 | 0 | 8       | 2 | 0 |  |

| 9                                  | 1 | 0 | 0 | 1 | 9       | 2 | 1 |  |

| 10                                 | 1 | 0 | 1 | 0 | 10      | 2 | 0 |  |

| 11                                 | 1 | 0 | 1 | 1 | 11      | 2 | 1 |  |

| 12                                 | 1 | 1 | 0 | 0 | 12      | 3 | 0 |  |

| 13                                 | 1 | 1 | 0 | 1 | 13      | 3 | 1 |  |

| 14                                 | 1 | 1 | 1 | 0 | 14      | 3 | 0 |  |

| 15                                 | 1 | 1 | 1 | 1 | 15      | 3 | 1 |  |

Table 2: Quaternary and binary input table.

J Electr Electron Syst

ISSN: 2332-0796 JEES

| Q  | Q  | Q, | Q <sub>2</sub> | Q <sub>3</sub> |

|----|----|----|----------------|----------------|

| 0, | 12 | 0  | 0              | 0              |

| 14 | 0  | 12 | 0              | 0              |

| 24 | 0  | 0  | 12             | 0              |

| 34 | 0  | 0  | 0              | 12             |

A LUT is an array indexing operator, where the output is mapped by the input, based on the configuration memory. The configuration values are initially stored in the LUT configuration memory, and according to the input, the logic value in the addressed position is assigned to the output (Figure 1).

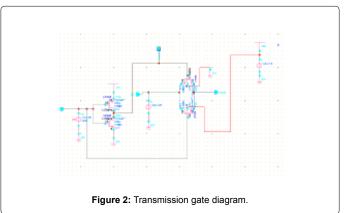

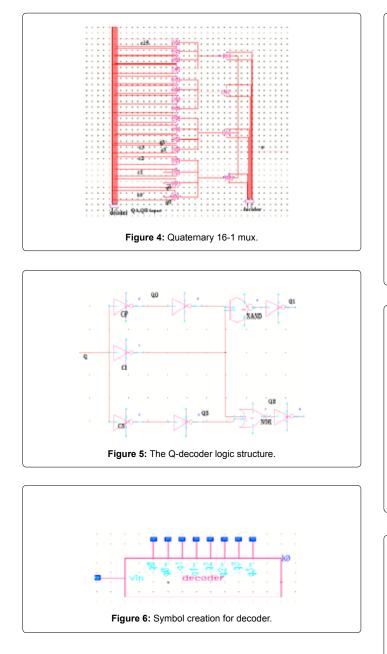

1V 16-1 MUX: A Multiplexer has many inputs and one output has to be selected. Although, the Use of quaternary logic helps to reduce the number of interconnecting wires, which leads to to a compact layout, with reduced routing capacitance. We used the typical value for a binary FPGA (10 pF), since it maintains same number of wires, we can increase the number of functions in FPGA [5].

When compared to binary quaternary implementation of 16-1 multiplexer had the less number of gates. For the binary implementation nearly 30 transmission gates are used but in case of quaternary only 24 transmission gates are used (Tables 2 and 3) (Figures 2-8).

### Quaternary-to-Binary converter

We also implemented the complete binary and quaternary look-

Page 2 of 4

# Citation: Sathyavathin S, Ilanthendral J (2015) A Novel Voltage-Mode Lut Using Clock Boosting Technique in Standard CMOS. J Electr Electron Syst 4: 139. doi:10.4172/2332-0796.1000139

up tables with the UMC 130 nm technology in order to evaluate their performance and power consumption. The development of the binary and quaternary LUTs was performed. Transistor widths were kept to the minimum value in order to have a fair comparison between binary and quaternary versions (Figure 9).

## Quaternery mux inputs and outputs waveforms

The quaternary structure proposed in this paper outperforms the binary implementation in both power consumption and propagation delay. These results were obtained through CADENCE Spectre simulation. The propagation delay is simply the largest delay from an input to the output of each LUT.

# Conclusion

In this paper, we have reported an innovative QLUT design that can be used for multiple valued combinational logic or as a building

Volume 4 • Issue 1 • 1000139

www.manaraa.com

Citation: Sathyavathin S, Ilanthendral J (2015) A Novel Voltage-Mode Lut Using Clock Boosting Technique in Standard CMOS. J Electr Electron Syst 4: 139. doi:10.4172/2332-0796.1000139

block in FPGAs. The QLUT internal functionality is implemented using simple standard CMOS structures. This feature is achieved through quaternary-to-binary decoders that quantize the input signals. This decoder is based on voltage-mode self-referenced comparators that allows the use of a standard CMOS Technology and overcomes previous design drawbacks. Also, a CB technique was used to decrease the switches resistance and increase the operation frequency, while at the same time, achieving low power consumption [6]. Therefore, the presented design is a valid solution to reduce the interconnections impact, without increasing Power consumption or losing performance. Experimental results were performed on an ASIC implementation of a full adder employing the designed QLUT. The obtained results attested the circuit feasibility and its advantages, using a standard CMOS process and its main characteristics (timing and power). References

Shang A, Kaviani S, Bathala K (2002) "Dynamic power consumption in virtex-II FPGA family," in Proc. ACM/SIGDA Int. Symp. Field-Program. Gate Arrays 157-164.

Page 4 of 4

- Zilic Z, Vranesic Z (1993) "Multiple-valued logic in FPGAs," in Proc. Midwest Symp. Circuits Syst 1553-1556.

- Ozer E, Sendag R, Gregg D (2006) Multiple-valued logic buses for reducing bus energy in low-power systems," IEE Comput. Digital Tech 153: 270-282.

- Current K (1994) "Current-mode CMOS multiple-valued logic circuits," IEEE J. Solid-State Circuits 29:-95-107.

- Kim J. (2010), "An area efficient multiplier using current-mode quaternary logic technique," in Proc. 10th IEEE Int. Solid-State Integr. Circuit Technol 403-405.

- Rabaey J (2009) Low Power Design Essentials (Integrated Circuits and Systems). New York, NY, USA: Springer-Verlag.