Pen-Chung Yew Jingling Xue (Eds.)

# Advances in Computer Systems Architecture

9th Asia-Pacific Conference, ACSAC 2004 Beijing, China, September 2004 Proceedings

Commenced Publication in 1973

Founding and Former Series Editors:

Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

## **Editorial Board**

David Hutchison

Lancaster University, UK

Takeo Kanade

Carnegie Mellon University, Pittsburgh, PA, USA

Josef Kittler

University of Surrey, Guildford, UK

Jon M. Kleinberg

Cornell University, Ithaca, NY, USA

Friedemann Mattern

ETH Zurich, Switzerland

John C. Mitchell

Stanford University, CA, USA

Moni Naor

Weizmann Institute of Science, Rehovot, Israel

Oscar Nierstrasz

University of Bern, Switzerland

C. Pandu Rangan

Indian Institute of Technology, Madras, India

Bernhard Steffen

University of Dortmund, Germany

Madhu Sudan

Massachusetts Institute of Technology, MA, USA

Demetri Terzopoulos

New York University, NY, USA

Doug Tygar

University of California, Berkeley, CA, USA

Moshe Y. Vardi

Rice University, Houston, TX, USA

Gerhard Weikum

Max-Planck Institute of Computer Science, Saarbruecken, Germany

Pen-Chung Yew Jingling Xue (Eds.)

# Advances in Computer Systems Architecture

9th Asia-Pacific Conference, ACSAC 2004 Beijing, China, September 7-9, 2004 Proceedings

#### Volume Editors

Pen-Chung Yew University of Minnesota at Twin Cities Department of Computer Science and Engineering Twin Cities, MN, USA E-mail: yew@cs.umn.edu

Jingling Xue

The University of New South Wales

School of Computer Science and Engineering

Sydney, NSW 2052, Australia

E-mail: jxue@cse.unsw.edu.au

Library of Congress Control Number: 2004111113

CR Subject Classification (1998): B.2, B.4, B.5, C.2, C.1, D.4

ISSN 0302-9743 ISBN 3-540-23003-3 Springer Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

Springer is a part of Springer Science+Business Media springeronline.com

© Springer-Verlag Berlin Heidelberg 2004 Printed in Germany

Typesetting: Camera-ready by author, data conversion by PTP-Berlin, Protago-TeX-Production GmbH Printed on acid-free paper SPIN: 11318651 06/3142 5 4 3 2 1 0

# **Preface**

On behalf of the program committee, we were pleased to present this year's program for ACSAC: Asia-Pacific Computer Systems Architecture Conference.

Now in its ninth year, ACSAC continues to provide an excellent forum for researchers, educators and practitioners to come to the Asia-Pacific region to exchange ideas on the latest developments in computer systems architecture. This year, the paper submission and review processes were semiautomated using the free version of CyberChair. We received 152 submissions, the largest number ever. Each paper was assigned at least three, mostly four, and in a few cases even five committee members for review. All of the papers were reviewed in a two-month period, during which the program chairs regularly monitored the progress of the review process. When reviewers claimed inadequate expertise, additional reviewers were solicited. In the end, we received a total of 594 reviews (3.9 per paper) from committee members as well as 248 coreviewers whose names are acknowledged in the proceedings. We would like to thank all of them for their time and effort in providing us with such timely and high-quality reviews, some of them on extremely short notice.

After all of the reviews were received, there was a one-week electronic program committee meeting during May 14 and May 21. All of the papers were reviewed and discussed by the program committee, and the final set of papers were selected. Program committee members were allowed to submit papers, but their papers were handled separately. Each of their papers was assigned to at least four committee members and reviewed under the same rigorous review process. The program committee accepted 7 out of 11 "PC" submissions. In the end, the program committee selected a total of 45 papers for this year's program with an acceptance rate close to 30%. Unfortunately, many fine papers could not be accommodated in this year's program because of our schedule.

In addition to the contributed papers, this year's program included invited presentations. We were very pleased that three distinguished experts accepted our invitation to share their views on various aspects of computer systems architecture design: James E. Smith (University of Winconsin-Madison, USA) on Some Real Observations on Virtual Machines, Jesse Z. Fang (Intel, USA) on A Generation Ahead of Microprocessor: Where Software Can Drive uArchitecture to?, and, finally, Guojie Li (Chinese Academy of Sciences, China) on Make Computers Cheaper and Simpler.

On behalf of the program committee, we thank all of the authors for their submissions, and the authors of the accepted papers for their cooperation in getting their final versions ready in time for the conference. We would also like to thank the Web Chair, Lian Li, for installing and maintaining CyberChair, and the Local Arrangements Chair, Wenguang Chen, for publicizing this conference.

Finally, we want to acknowledge the outstanding work of this year's program committee. We would like to thank them for their dedication and effort

## VI Preface

in providing timely and thorough reviews for the largest number of submissions ever in our conference history, and their contribution during the paper selection process. It was a great pleasure working with these esteemed members of our community. Without their extraordinary effort and commitment, it would have been impossible to put such an excellent program together in a timely fashion. We also want to thank all our sponsors for their support of this event. Last, but not least, we would like to thank the General Chair, Weimin Zheng for his advice and support to the program committee and his administrative support for all of the local arrangements.

June 2004

Pen-Chung Yew Jingling Xue

# Conference Organization

# General Chair

Weimin Zheng Tsinghua University, China

# **Program Chairs**

Pen-Chung Yew University of Minnesota, USA

Jingling Xue University of New South Wales, Australia

# Local Arrangements Chair

Wenguang Chen Tsinghua University, China

# Local Arrangements Committee

Hongliang Yu Tsinghua University, China Jianian Yan Tsinghua University, China Jidong Zhai Tsinghua University, China Ruini Xue Tsinghua University, China Tsinghua University, China Tsinghua University, China

# Web Chair

Lian Li

University of New South Wales, Australia

# **Program Committee**

Lars Bengtsson Sangyeun Cho Lynn Choi

Rudolf Eigenmann Jean-Luc Gaudiot Antonio Gonzalez

Gernot Heiser Wei-Chung Hsu Chris Jesshope

Angkul Kongmunyattana

Feipei Lai Zhiyong Liu

Guei-Yuan Lueh John Morris

Tadao Nakamura Yukihiro Nakamura Amos Omondi Lalit M. Patnaik Jih-Kwon Peir Ronald Pose Depei Qian

Stanislav G. Sedukhin Naofumi Takagi Zhimin Tang Rajeev Thakur Theo Ungerer Winfried W. Wilcke Weng Fai Wong

Chengyong Wu Ming Xu

Yuanyuan Yang

Rumi Zahir Chuanqi Zhu Chalmers University of Technology, Sweden

Samsung Electronics, Co., Korea

Korea University, Korea Purdue University, USA

University of California, Irvine, USA Universitat Politecnica de Catalunya

& Intel Labs, Spain

National ICT Australia, Australia University of Minnesota, USA

University of Hull, UK

University of Nevada, Reno, USA National Taiwan University

National Natural Science Foundation

of China, China Intel, USA

Chung-Ang University, Korea

& University of Auckland, New Zealand

Tohoku University, Japan Kyoto University, Japan Flinders University, Australia

Indian Institute of Science, Bangalore, India

University of Florida, USA Monash University, Australia Xian Jiaotong University, China University of Aizu, Japan

Nagoya University, Japan

Chinese Academy of Sciences, China Argonne National Laboratory, USA University of Augsburg, Germany

IBM Research, USA

National University of Singapore, Singapore

Chinese Academy of Sciences, China

National University of Defense Technology,

China

State University of New York at Stony Brook,

USA

Intel, USA

Fudan University, China

# Co-reviewers

Tom Adelmeyer

Alex Aletà

Jalal Almhana

Madhusudhanan Anantha

Juan Luis Aragon Brian Armstrong Eduard Ayguade Faruk Bagci

Nitin Bahadur

Vishwanath P. Baligar

Bin Bao

Ayon Basumallik Jürgen Beckeer Ramón Beivide Bryan Black Tatiana Bokareva Uwe Brinkschulte Ralph Butler

Luis M. Díaz de Cerio

Jason Chang

Yen-Jen Chang

Mei Chao

Cheng Chen

Dong-Yuan Chen

Gen-Huey Chen

Haibo Chen

Howard Chen

Ronghua Chen

Tien-Fu Chen

Wen-Hsien Chen Wenguang Chen Yinwen Chen Yung-Chiao Chen

Seng-Cho Chou Yang Wai Chow

Peter Chubb C.G. Chung

Avery Ching

Chung-Ping Chung Sung Woo Chung Josep M. Codina Tim Conrad Nawal Copty

Julita Corbalan

Toni Cortes

Alfredo Cristobal-Salas

Abhinav Das Xiaotie Deng Qiang Ding Yingfei Dong

Klaus Dorfmüller-Ulhaas

David Du Colin Egan Kevin Elphinstone Dongrui Fan Hao Feng

Konrad Froitzheim

Rao Fu

Antonia Gallardo Boon-Ping Gan Enric Gibert Marc Gonzalez Charles Gray Yi Guo Weili Han

Wessam Hassanein

Guojin He Gerolf Hoflehner Scott Hoyte Pao-Ann Hsiung

Wen Hu Dandan Huan Ing-Jer Huang Junwei Huang Lei Huang Yi-Ping Hung Wei Huo

Tomonori Izumi

Muhammad Mahmudul Islam

Yaocang Jia Hong Jiang Weihua Jiang Yi Jiang

Troy A. Johnson Edward Sim Joon Sourabh Joshi

Rov Ju

Marcelo E. Kaihara

# X Organization

Dongsoo Kang Ryosuke Kato Jörg Keller Ihn Kim JinPyo Kim Sunil Kim Chung-Ta King Jon Krueger

Fumio Kumazawa Ihor Kuz Atul Kwatra

Hsiu-Hui Lee Hung-Chang Lee Sanghoon Lee Yong-fong Lee Jianping Li

Jie Li Shengjun Li Wei Li

Yingsheng Li Yunchun Li Weifa Liang Shih-wei Liao Wanjiun Liao Björn Liljeqvist Ching Lin

Fang-Chang Lin Fang-Pang Lin Hung-Yau Lin Shian-Hua Lin Xiaobin Lin Bin Liu

Chen Liu Jiangchuan Liu Jyi-shane Liu Michael Liu Tao Liu Zhanglin Liu

Jiwei Lu Peng Lu

Zhongzhi Luan Jesus Luna Yuh-Dauh Lyuu Takahiko Masuzaki

Ryusuke Miyamoto

Chi Ma Xiaosong Ma Erik Maehle

Mike Mesnier Neill Miller

Do Quang Minh Dave Minturn Steven Molnar

Rafael Moreno-Vozmediano

Alberto J. Munoz

Hashem Hashemi Najaf-abadi

Gil Neiger Anindya Neogi Tin-Fook Ngai Qizhi Ni Rong Ni Hiroyuki Ochi Robert Olson Ming Ouhyoung

Deng Pan Zhelong Pan

Marina Papatriantafilou

Chan-Ik Park

Gi-Ho Park

Junho Park

Enric Pastor

Jan Petzold

Matthias Pfeffer

Andy D. Pimentel

Dhiraj Pradhan

Nol Premasathian

Rolf Rabenseifner

Ryan Rakvic

Rajiv Ranjan

Xiaojuan (Joanne) Ren

Won Woo Ro Shanq-Jang Ruan

Hariharan Sandanagobalane

Kentaro Sano Hartmut Schmeck Ioannis T. Schoinas Peter Schulthess André Seznec Hemal Shah

Shrikant Shah

Hong Shen Sameer Shende Jang-Ping Sheu Xudong Shi Mon-Chau Shie Yong Shin

Tsan-sheng Shsu

Siew Sim

Mostafa I. Soliman James Stichnoth

Feiqi Su Yeali Sun Kosuke Tsujino Hiroshi Tsutsui Kazuyoshi Takagi Akihito Takahashi Shigeyuki Takano

Santipong Tanchatchawal

Wei Tang

Hariharan L. Thantry Ekkasit Tiamkaew Apichat Treerojporn Kun-Lin Tsai Sascha Uhrig Gladys Utrera

Alexander Vazhenin

Xavier Vera

Murali Vilayannur Harsh Vipat Jian Wang Kuochen Wang Peng Wang Qin Wang

ShengYue Wang Xiaodong Wang Ye Wang Yanzhi Wen Sung-Shun Weng Adam Wiggins Weng-Fai Wong Hsiaokuang Wu Hui Wu

Jiajun Wu

Jiajun Wu

Jiesheng Wu

Meng-Shiou Wu

Youfeng Wu

CanWen Xiao

Dai Xiao

Junhua Xiao

Yang Xiao

Wenjun Xiao

Jinhui Xu

Chu-Sing Yang

Xu Yang

Zhen Yang

Zhen Yang

Handong Ye

Chingwei Yeh

Kyueun Yi

Heng Zhang

Hongjiang Zhang

Hui Zhang

Minjie Zhang

Weihua Zhang

Xiaomin Zhang

Xingjun Zhang

Zhenghao Zhang

Qin Zhao Yili Zheng Yuezhi Zhou Jiahua Zhu

# Table of Contents

| Keynote Address I                                                                                                                                   |     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Some Real Observations on Virtual Machines                                                                                                          | 1   |

| Session 1A: Cache and Memory                                                                                                                        |     |

| Replica Victim Caching to Improve Reliability of In-Cache Replication                                                                               | 2   |

| Efficient Victim Mechanism on Sector Cache Organization                                                                                             | 16  |

| Cache Behavior Analysis of a Compiler-Assisted Cache Replacement Policy                                                                             | 30  |

| Modeling the Cache Behavior of Codes<br>with Arbitrary Data-Dependent Conditional Structures                                                        | 44  |

| Session 1B: Reconfigurable and Embedded<br>Architectures                                                                                            |     |

| A Configurable System-on-Chip Architecture for Embedded Devices $Sebastian\ Wallner$                                                                | 58  |

| An Auto-adaptative Reconfigurable Architecture for the Control                                                                                      | 72  |

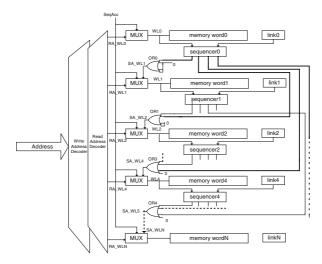

| Enhancing the Memory Performance of Embedded Systems with the Flexible Sequential and Random Access Memory                                          | 88  |

| Heuristic Algorithm for Reducing Mapping Sets of Hardware-Software Partitioning in Reconfigurable System  Seong-Yong Ahn, Jun-Yong Kim, Jeong-A Lee | 102 |

| الكالكا (2 للاستشار                                                                                                                                 |     |

| Session 2A: Processor Architecture and Design I                                                                                              |     |

|----------------------------------------------------------------------------------------------------------------------------------------------|-----|

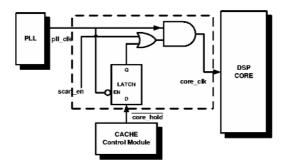

| Architecture Design of a High-Performance 32-Bit Fixed-Point DSP $\it Jian\ Chen,\ Ruhao\ Xu,\ Yuzhuo\ Fu$                                   | 115 |

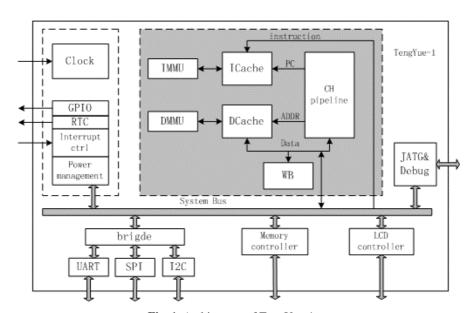

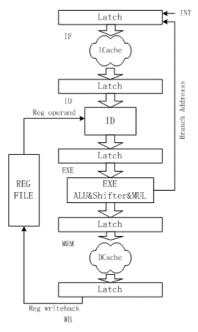

| TengYue-1: A High Performance Embedded SoC                                                                                                   | 126 |

| A Fault-Tolerant Single-Chip Multiprocessor                                                                                                  | 137 |

| Session 2B: Power and Energy Management                                                                                                      |     |

| Initial Experiences with Dreamy Memory and the RAMpage Memory Hierarchy                                                                      | 146 |

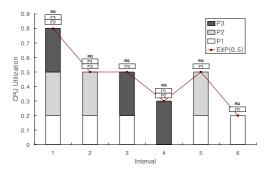

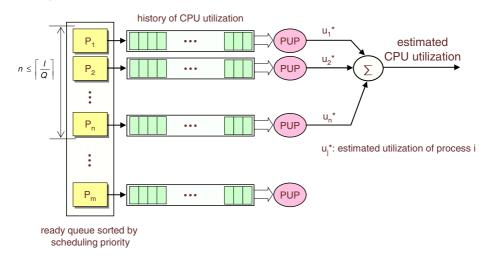

| dDVS: An Efficient Dynamic Voltage Scaling Algorithm Based on the Differential of CPU Utilization                                            | 160 |

| High Performance Microprocessor Design Methods Exploiting Information Locality and Data Redundancy for Lower Area Cost and Power Consumption | 170 |

| Session 3A: Processor Architecture and Design II                                                                                             |     |

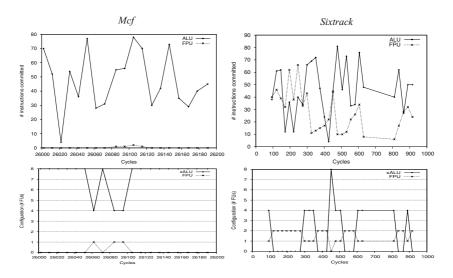

| Dynamic Reallocation of Functional Units in Superscalar Processors Marc Epalza, Paolo Ienne, Daniel Mlynek                                   | 185 |

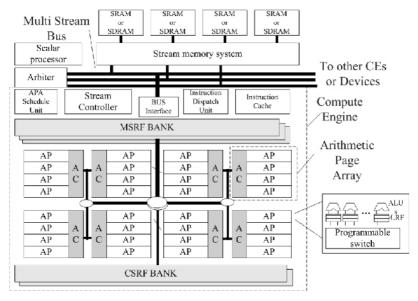

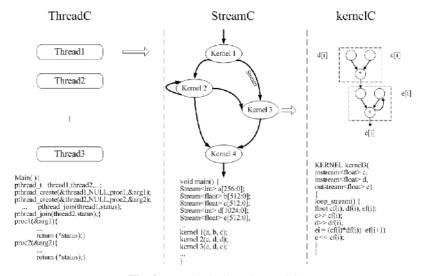

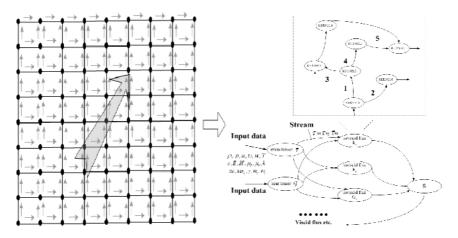

| Multiple-Dimension Scalable Adaptive Stream Architecture                                                                                     | 199 |

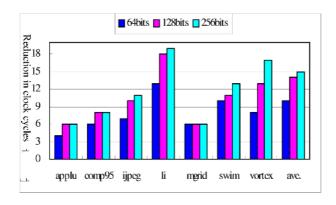

| Impact of Register-Cache Bandwidth Variation on Processor Performance                                                                        | 212 |

| Session 3B: Compiler and Operating System Issues                                                                                             |     |

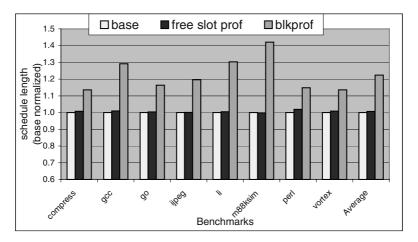

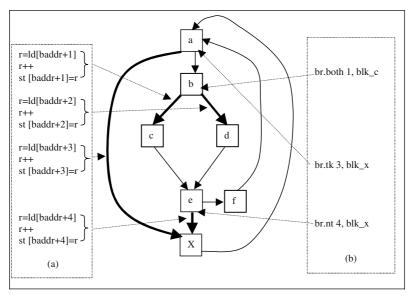

| Exploiting Free Execution Slots on EPIC Processors for Efficient and Accurate Runtime Profiling                                              | 226 |

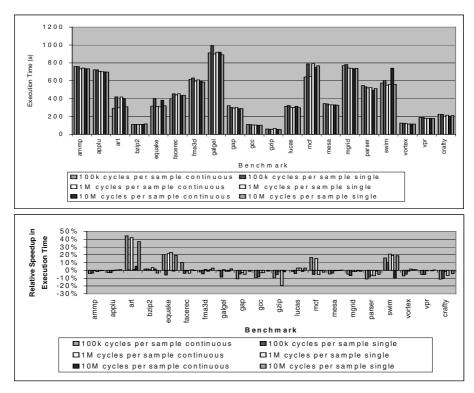

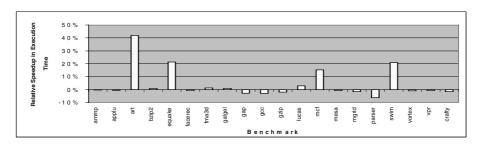

| Continuous Adaptive Object-Code Re-optimization Framework                                                                                    | 241 |

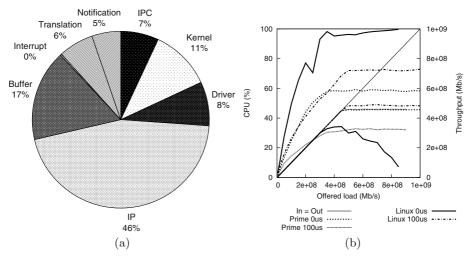

| Initial Evaluation of a User-Level Device Driver Framework                                                                                   | 256 |

| Keynote Address II                                                                                                                           |     |

|----------------------------------------------------------------------------------------------------------------------------------------------|-----|

| A Generation Ahead of Microprocessor:  Where Software Can Drive uArchitecture To?  Jesse Z. Fang                                             | 270 |

| Session 4A: Application-Specific Systems                                                                                                     |     |

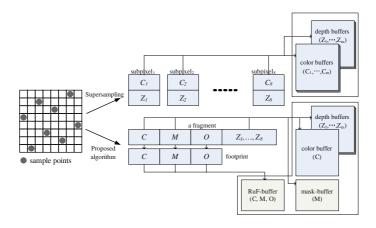

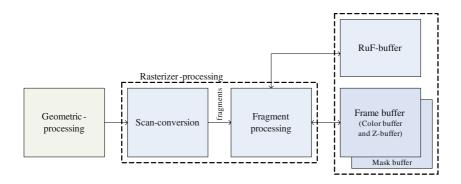

| A Cost-Effective Supersampling for Full Scene AntiAliasing                                                                                   | 271 |

| A Simple Architectural Enhancement for Fast and Flexible Elliptic Curve Cryptography over Binary Finite Fields $\mathrm{GF}(2^m)$            | 282 |

| Scalable Design Framework for JPEG2000 System Architecture                                                                                   | 296 |

| Real-Time Three Dimensional Vision                                                                                                           | 309 |

| Session 4B: Interconnection Networks                                                                                                         |     |

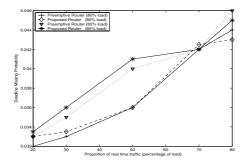

| A Router Architecture for QoS Capable Clusters                                                                                               | 321 |

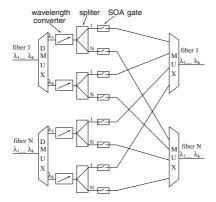

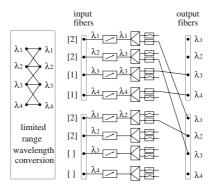

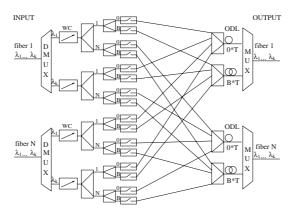

| Optimal Scheduling Algorithms in WDM Optical Interconnects with Limited Range Wavelength Conversion Capability Zhenghao Zhang, Yuanyuan Yang | 335 |

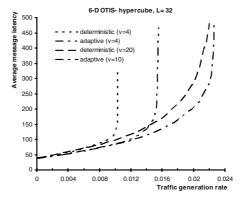

| Comparative Evaluation of Adaptive and Deterministic Routing in the OTIS-Hypercube                                                           | 349 |

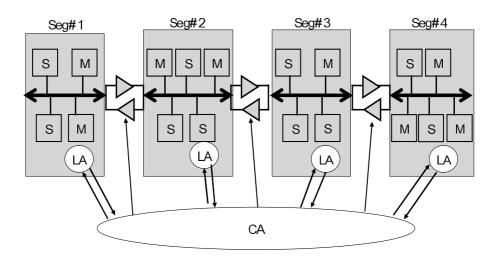

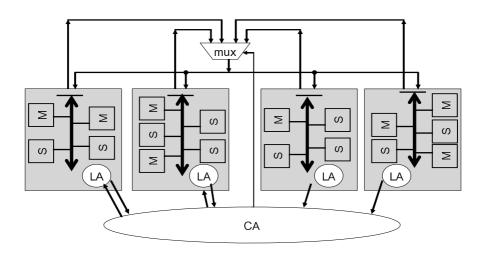

| A Two-Level On-Chip Bus System Based on Multiplexers                                                                                         | 363 |

| Keynote Address III                                                                                                                          |     |

| Make Computers Cheaper and Simpler                                                                                                           | 373 |

| Session 5A: Prediction Techniques                                                                        |     |

|----------------------------------------------------------------------------------------------------------|-----|

| A Low Power Branch Predictor to Selectively Access the BTB                                               | 374 |

| Static Techniques to Improve Power Efficiency of Branch Predictors Weidong Shi, Tao Zhang, Santosh Pande | 385 |

| Choice Predictor for Free                                                                                | 399 |

| Performance Impact of Different Data Value Predictors                                                    | 414 |

| Session 5B: Parallel Architecture and Programming                                                        |     |

| Heterogeneous Networks of Workstations                                                                   | 426 |

| Finding High Performance Solution in Reconfigurable Mesh-Connected VLSI Arrays                           | 440 |

| Order Independent Transparency<br>for Image Composition Parallel Rendering Machines                      | 449 |

| An Authorization Architecture Oriented to Engineering and Scientific Computation in Grid Environments    | 461 |

| Session 6A: Microarchitecture Design and Evaluations                                                     |     |

| Validating Word-Oriented Processors for Bit and Multi-word Operations                                    | 473 |

| Dynamic Fetch Engine for Simultaneous Multithreaded Processors                                           | 489 |

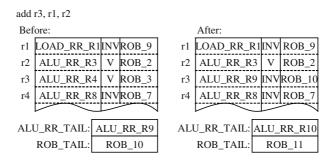

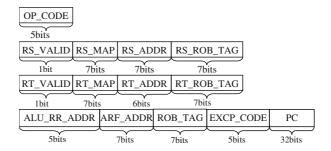

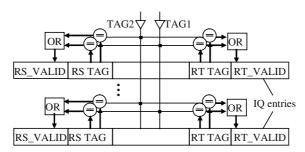

| A Novel Rename Register Architecture and Performance Analysis Zhenyu Liu, Jiayue $Qi$                    | 503 |

| Session 6B: Memory and I/O Systems                                                                       |     |

| A New Hierarchy Cache Scheme Using RAM and Pagefile                                                      | 515 |

| An Object-Oriented Data Storage System on Network-Attached Object Devices                  | 527 |

|--------------------------------------------------------------------------------------------|-----|

| A Scalable and Adaptive Directory Scheme for Hardware Distributed Shared Memory            | 539 |

| Session 7A: Potpourri                                                                      |     |

| A Compiler-Assisted On-Chip Assigned-Signature Control Flow Checking                       | 554 |

| A Floating Point Divider Performing IEEE Rounding and Quotient Conversion in Parallel      | 568 |

| Efficient Buffer Allocation for Asynchronous Linear Pipelines by Design Space Localization | 582 |

| Author Index                                                                               | 597 |

# Some Real Observations on Virtual Machines

James E. Smith

Department of Electrical and Computing Engineering University of Wisconsin-Madison jes@ece.wisc.edu

Abstract. Virtual machines can enhance computer systems in a number of ways, including improved security, flexibility, fault tolerance, power efficiency, and performance. Virtualization can be done at the system level and the process level. Virtual machines can support high level languages as in Java, or can be implemented using a low level co-designed paradigm as in the Transmeta Crusoe. This talk will survey the spectrum of virtual machines and discuss important design problems and research issues. Special attention will be given to co-designed VMs and their application to performance- and power-efficient microprocessor design.

# Replica Victim Caching to Improve Reliability of In-Cache Replication

W. Zhang

Dept of ECE, SIUC, Carbondale, IL 62901, USA zhang@engr.siu.edu

Abstract. Soft error conscious cache design is a necessity for reliable computing. ECC or parity-based integrity checking techniques in use today either compromise performance for reliability or vice versa. The recently-proposed ICR (In-Cache Replication) scheme can enhance data reliability with minimal impact on performance, however, it can only exploit a limited space for replication and thus cannot solve the conflicts between the replicas and the primary data without compromising either performance or reliability. This paper proposes to add a small cache, called replica victim cache, to solve this dilemma effectively. Our experimental results show that a replica victim cache of 4 entries can increase reliability of L1 data caches 21.7% more than ICR without impacting performance, and the area overhead is within 10%.

# 1 Introduction and Motivation

Soft errors are unintended transitions of logic states caused by external radiations such as alpha particle and cosmic ray strikes. Recent studies [4,6,5,9] indicate that soft errors are responsible for a large percentage of computation failures. In current microprocessors, over 60% of the on-chip estate is taken by caches, making them more susceptible to external radiations. The soft errors in cache memories can easily propagate into the processor registers and other memory elements, resulting in catastrophic consequences on the execution. Therefore, soft error tolerant cache design is becoming increasingly important for failure-free computation.

Information redundancy is the main technique to improve data integrity. Currently the popular information redundancy scheme for memories is either byte-parity (one bit parity per 8-bit data) [1], or single error correcting-double error detecting (SEC-DED) code (ECC)[2,3]. However, both of these two schemes have deficiencies. Briefly, parity check can only detect single-bit errors. While SEC-DEC based schemes can correct single-bit errors and detect two-bit errors, they can also increase the access latency of the L1 cache, and thus not suitable for high-end processors clocked over 1GHz [7]. Recently, an approach called ICR (In-Cache Replication) has been proposed to enhance reliability of the L1 data cache for high-performance processors [7]. The idea of ICR is to exploit "dead" blocks in the L1 data cache to store the replicas for "hot" blocks so that a large percentage of read hits in the L1 can find their replicas in the same cache, which

can be used to detect and correct single bit and/or multiple bit errors. While the ICR approach can achieve a better tradeoff between performance and reliability than parity-only or ECC-only protection, it can only exploit a limited space (namely the "dead" blocks in the data cache) for replication. In addition, since the replica and the primary data are stored in the same cache, they inevitably have conflicts with each other. The current policy adopted by ICR [7] is to give priority to the primary data for minimizing the impact on performance. In other words, the data reliability is compromised. As illustrated in [7], 10% to 35% of data in the L1 data cache is not protected (i.e. having no replicas) by ICR schemes, which may cause severe consequences in computation and thus are not useful for applications that require high reliability or operate under highly noisy environments.

This paper proposes a novel scheme to enhance the reliability of ICR further by adding a small fully-associative cache to store the replica victims, which is called the replica victim cache in this paper. Unlike the victim cache proposed by jouppi [10] for reducing the conflict misses for a direct-mapped cache without In-Cache Replication, the proposed replica victim cache is utilized to store the replica victims, which are conflicting with the primary data or other replicas in the primary data cache, for enhancing reliability of the ICR approaches significantly without compromising performance. Moreover, since the replica is used to improve data integrity, the replica victim cache does not need to swap the replica with the primary data when accessed. In contrast, the traditional victim cache stores different data (i.e., victim) from the primary cache, and the victims need to be swapped to the L1 cache in the case of a miss in the L1 data cache that hits in the victim cache[10]. The paper examines the following problems.

- 1. How does reliability, in terms of loads with replica (see the definition in 4), relate to the size of the replica victim cache, the size and associativity of the primary cache? How much loads with replica can be increased by the addition of a replica victim cache?

- 2. How to exploit the replicas in either the primary cache or the replica victim cache to provide different levels of reliability and performance?

- 3. What is the error detection and correction behavior of different replica-based schemes under different soft error rates?

We implemented the proposed replica victim caching schemes by modifying the Simplesclar 3.0 [14]. The error injection experiments are based on *random injection model* [5]. Our experimental results reveal that a replica victim cache of 4 entries can increase the reliability of ICR by 21.7% without impacting performance and its area overhead is less than 10%, compared to most L1 data caches.

The rest of the paper is organized as follows. Section 2 introduces the background information about In-Cache Replication and its limitation. Section 3 describes the architecture of replica victim caching and different schemes to exploit the replica victim lines for improving data reliability. The evaluation methodology is given in section 4. Section 5 presents the experimental results. Finally,

#### W. Zhang

4

section 6 summarizes the contributions of this paper and identifies directions for future research.

# 2 Background and Motivation

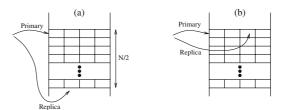

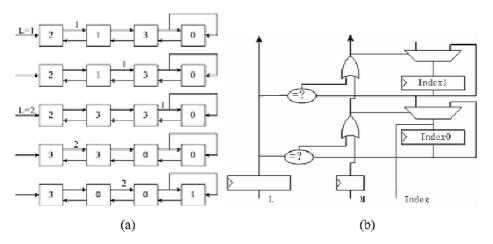

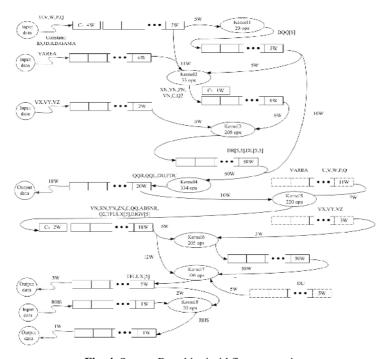

A recent paper [7] presents ICR (In-Cache Replication) for enhancing data cache reliability without significant impact on performance. The idea of ICR is to replicate hot cache lines in active use within the dead cache lines. The mapping between the primary data and the replica is controlled by a simple function. Two straightforward mapping functions are studies in [7], namely, the vertical mapping (replication across sets) and the horizontal mapping (replication within the ways of a set) [7], as shown in figure 1. The dead cache lines are predicted by a time-based dead block predictor, which is shown to be highly accurate and has low hardware overhead [8]. The ICR approach can be used either with parity or ECC based schemes and there is a large design space to explore, including what, when and where to replicate the data, etc [7]. The design decisions adopted in this paper is presented in table 1.

The results in [7] demonstrate that the ICR schemes can achieve better performance and/or reliability than the schemes that use ECC or parity check alone, however, it can only achieve modest reliability improvement due to the limited space it can exploit. Since each L1 data cache has a fixed number of cache lines, and each cache line can be either used to store the primary data to benefit performance or to store the replicas for enhancing data reliability, ICR approaches

Fig. 1. Cache line replication (a) vertical replication (b) horizontal replication [7].

| Table | 1 Default  | implementation | stratogics | rogarding | anaha | line replication |

|-------|------------|----------------|------------|-----------|-------|------------------|

| Table | 1. Delault | mplementation  | strategres | regarding | cache | mie replication. |

| Question                                    | Answer                                                                                                                             |

|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| When do we replicate?                       | Only during writes                                                                                                                 |

| Where do we replicate?                      | N/2 sets away from the primary location                                                                                            |

| How many times do we attempt replication?   | Once for each write                                                                                                                |

| How many replicas do we create?             | At most 1 per line                                                                                                                 |

| How do we protect unreplicated cache lines? | Using parity                                                                                                                       |

| How do we protect replicated cache lines?   | Using parity or parallel comparison between<br>the primary data and its replica, depending on<br>the scheme we use (see section 3) |

| How do we place a replica in a set?         | Candidates include both dead lines<br>and replicas (we check the dead lines first)                                                 |

| What needs to be done upon a replacement?   | We remove replica as well                                                                                                          |

give priority to performance by using several strategies. Firstly, the dead block predictor is designed to be very accurate so that the blocks predicted dead will most likely not be accessed in the near future. Otherwise, the primary data has to be loaded from the higher level memory hierarchy, resulting in performance penalty. Secondly, in case of a conflict between the primary data and the replica, ICR gives higher priority to the primary data and the replica is simply discarded. For instance, when a primary data is written to a cache block, which stores a replica for another primary data, the replica will be overwritten by the coming primary data. As a result, ICR approach can only the replicas that do not conflict with the primary data, resulting in moderate data reliability improvement. The experiments in [7] also reveal that 10% to 35% of load hits in L1 cannot find their replicas and ICR schemes have more than 20% unrecoverable loads under intense error injection. With the trend of increasing soft error rate, the reliability of ICR approaches need to be improved further, especially for applications that demand very high data reliability or operate under highly-noisy environments.

# 3 Replica Victim Cache

While one straightforward way to enhance data reliability of ICR further is to make more replicas in the L1 data cache by giving priority to replicas in case of their conflicts with the primary data. This approach, however, can inevitably degrade performance and thus is not acceptable. Another approach used in mission-critical applications is the NMR (N Modular Redundancy) scheme, which replicate the data cache for multiple times. However, the NMR scheme is too costly for microprocessors or embedded system with cost and area constraint.

This paper proposes an approach to enhance data reliability of ICR without performance degradation or significant area overheads. The idea is to add a small fully-associative replica victim cache to store the replica victim lines whenever they are conflicting with primary cache lines. Due to the fully associativity of the replica victim cache and data locality (replicas also exhibit temperal and spatial locality, since they are the "images" of the primary data), a very large percentage of load hits in the L1 can find their replicas available either in the L1 data cache or in the replica victim cache.

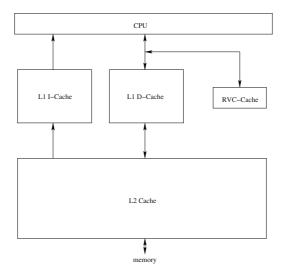

Victim cache is not a new idea in cache design. Jouppi proposed the victim cache to store the victim lines evicted from the L1 cache for reducing the conflict misses [10]. However, the victim cache proposed by Jouppi cannot be used to enhance data reliability, since there is no redundant copies in both the L1 cache and the victim cache (i.e., only the blocks evicted from the L1 are stored in the victim cache). While the original victim cache aims at performance enhancement, the objective of the replica victim cache is to improve data integrity of ICR approaches significantly without impacting performance. The replica victim cache is a small fully associative cache in parallel with the L1 data cache, as shown in figure 2. In addition to In-Cache Replication, the replica victim cache is used to store replicas for the primary data in the L1 in the following cases:

1. There is no dead block available in the L1 data cache to store the replica.

Fig. 2. The architecture of replica victim cache.

- 2. The replica is replaced by the primary data since ICR gives priority to the primary data.

- 3. The replica is replaced by another replica for another primary data (note that for a set-associative data cache, multiple replicas can be mapped to the same dead block with ICR approach [7]).

Since ECC computation has performance overhead, we assume all the cache blocks of the L1 and the replica victim cache are protected by parity check. The replicas (both in the replica victim cache and the L1 data cache due to ICR) can be read at each read hits in the L1 for parallel comparison with the primary data to detect multiple bit errors. Alternatively, the replicas can be read only when the parity bit of the primary data indicates an error. The former scheme can enhance data reliability greatly, but there is a performance penalty for the parallel comparison. We assume it takes 1 extra cycle to compare the primary data and the replica in our simulations. The latter scheme also improve the reliability by being able to recover from single bit errors.

The paper examines the following problems.

- 1. How does the reliability, in terms of loads with replica (see 4), relate to the size of the replica victim cache, the size and associativity of the primary cache? How much loads with replica can be increased by the addition of a replica victim cache?

- 2. How to exploit the replicas in either the primary cache or the replica victim cache to provide different levels of reliability and performance?

- 3. How does the error detection and correction behavior of different replicabased schemes under different soft error rates?

To answer the above questions, we propose and evaluate the following schemes:

- BaseP: This is a normal L1 data cache without the replica victim cache.

All cache blocks are protected by parity. The load and store operations are modeled to take 1 cycle in our experiments.

- BaseECC: This scheme is similar to BaseP scheme except that all cache blocks are protected by ECC. Store operations still take 1 cycle (as the writes are buffered), but loads take 2 cycles to account for the ECC verification.

- RVC-P: This scheme implements the In-Cache Replication and the proposed replica victim caching. When there is a conflict between the primary data and the replica, the replica victim is stored to the replica victim cache. If the replica victim cache is full, the least-recently used replica is discarded. All cache blocks are protected by parity and the replica is only checked if the parity bit of the primary data indicates an error. Load and store operations are modeled to take 1 cycle in our experiments.

- RVC-C: This scheme is similar to RVC-P scheme except that the replica is compared with the primary data before the load returns. The search of replica can be executed simultaneously in both the L1 data cache and the replica victim cache. If the replica hits in the L1 data cache, that replica is used to compare with the primary data; otherwise, the replica in the replica victim cache is used for comparison if there is a hit in the replica victim cache. Note that we give priority to the replicas found in the L1 data cache, because the L1 contains the most updated replicas while the replica victim cache may not (because it only contains the most updated replica victims). However, for the given primary data, if its replica cannot be found in the L1 data cache, the replica found in the replica victim cache must contain the most updated value because every replica victim of the data must have been written to the replica victim cache. We conservatively assume that the load operations take 2 cycles, and store operations take 1 cycle as usual.

It should be noted that in addition to parity check and ECC, the writethrough cache and speculative ECC loads are also widely employed for improving data reliability. For write-through caches, data redundancy is provided by propagating every write into the L2 cache. However, write-through caches increase the number of writes to the L2 dramatically, resulting in the increase of write stalls even with a write-buffer. Thus both performance and energy consumption can be impacted [7]. Another way to improve data reliability while circumventing the ECC time cost is the speculative ECC load scheme, which performs the ECC checks in the background while data is loaded and the computation is allowed to proceed speculatively. While speculative ECC loads can potentially hide the access latency, it is difficult to stop the error propagation in a timely manner and may result in high error recovery cost. Since ECC computation consumes more energy than parity check, it is also shown that speculative ECC load has worse energy behavior than the ICR approach that uses parity check only (i.e., ICR-P-PS) [7]. Due to these reasons, we focus on investigating approaches to improve reliability for write-back data caches, and we only compare our approach directly with the recently-proposed ICR approaches, which have exhibited better

performance and/or energy behavior than the write-through L1 data cache and the speculative ECC load [7].

# 4 Evaluation Methodology

#### 4.1 Evaluation Metrics

To compare performance and reliability of different schemes, we mainly use the following two metrics:

- Execution Cycles is the time taken to execute 200 million application instructions.

- Loads with Replica is the metric proposed in [7] to evaluate the reliability enhancement for data caches. A higher loads with replica indicates higher data reliability, as illustrated by error injection experiments [7]. Since we add a replica victim cache to the conventional L1 data cache architecture, we modify the definition of loads with replica proposed in [7] to be the fraction of read hits that also find their replicas either in the L1 data cache or in the replica victim cache. Note that the difference between our definition and the definition in [7] is that in our scheme, the replica of "dirty" data can be found either in the L1 data cache or in the replica victim cache; while in the ICR scheme [7], the replicas can be only found in the L1 data cache.

# 4.2 Configuration and Benchmarks

We have implemented the proposed replica victim caching schemes by modifying the Simplesclar 3.0 [14]. We conduct detailed cycle level simulations with sim-outorder to model a multiple issue superscalar processor with a small fully-associative replica victim cache. The default simulation values used in our experiments are listed in Table 2 (note that we do not list the configuration of the replica victim cache in Table 2, since we need to make experiments with different replica cache size).

We select ten applications from the SPEC 2000 suite [16] for this evaluation. Since the simulations of these applications are extremely time consuming, we fast forward the first half billion instructions and present results for the next 200 million instructions. Important performance characteristics of these applications in the base scheme are given in Table 3.

## 5 Results

# 5.1 The Size of the Replica Victim Cache and Data Integrity Improvement

Our first experiment is to investigate what is the appropriate size for the replica victim cache. On one hand, the replica victim cache must be small to minimize

**Table 2.** Configuration parameters in our base configuration for a superscalar architecture. All caches are write-back.

| Configuration Parameter | Value                                        |

|-------------------------|----------------------------------------------|

|                         | Processor                                    |

| Functional Units        | 4 IALUs, 4FPU                                |

| LSQ Size                | 8 Instructions                               |

| RUU Size                | 16 Instructions                              |

| Fetch Width             | 4 instructions/cycle                         |

| Decode Width            | 4 instructions/cycle                         |

| Issue Width             | 4 instructions/cycle                         |

| Commit Width            | 4 instructions/cycle                         |

| Fetch Queue Size        | 4 instructions                               |

| Cycle Time              | 1ns                                          |

| Cache a                 | nd Memory Hierarchy                          |

| L1 Instruction Cache    | 16KB, 1-way, 32 byte blocks, 1 cycle latency |

| L1 Data Cache           | 16KB, 4-way, 32 byte blocks, 1 cycle latency |

| L2                      | 256K, 4-way, 64 byte blocks, 6 cycle latency |

| Memory                  | 100 cycle latency                            |

**Table 3.** Benchmarks from SPEC2000. The last column give the execution cycles for Base scheme.

| Benchmark  | Description                         | Number of       | Number of    | Execution Cycles |

|------------|-------------------------------------|-----------------|--------------|------------------|

| Name       |                                     | Data References | Cache Misses | of Base          |

| 164.gzip   | Compression                         | 58582206        | 1167237      | 129215053        |

| 175.vpr    | FPGA circuit placement and routing  | 87602536        | 1968330      | 202606221        |

| 176.gcc    | C programming language compiler     | 79860452        | 982483       | 220017658        |

| 181.mcf    | Combinational optimization          | 112113406       | 10423182     | 240140816        |

| 255.vortex | Object-oriented database            | 110330626       | 1591461      | 231793925        |

| 256.bzip2  | Compression                         | 96251361        | 1550219      | 134186684        |

| 177.mesa   | 3D graphics library                 | 98933099        | 224339       | 199721006        |

| 179.art    | C Image recognition/neural networks | 87569639        | 7144640      | 236659516        |

| 183.equake | Seismic wave propagation simulation | 64742897        | 373522       | 118643743        |

| 188.ammp   | C Computational chemistry           | 118184707       | 15826817     | 354806058        |

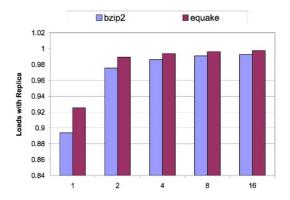

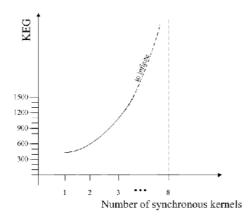

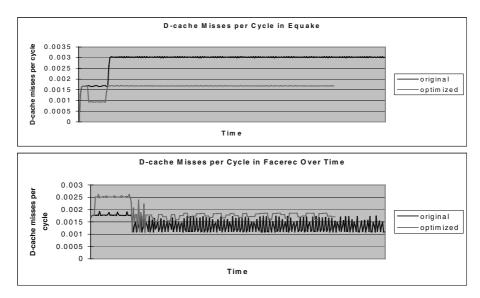

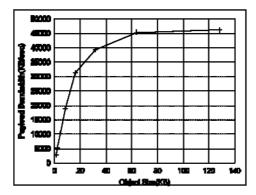

the hardware overheads. On the other hand, the replica victim cache should be large enough to accommodate the replica victims as many as possible. Due to data locality, it is possible to use a small replica victim cache to store the replica victims for the data, which is most likely accessed in the future. We use an empirical approach to find the best size for the replica victim cache. Specifically, we make experiments on two randomly selected benchmarks (i.e., bzip2 and equake) for replica victim caches with different sizes varying from 1 block to 16 blocks and the L1 data cache is fixed to be 16K-Byte, 4-way set associative, as given in table 2. The loads with replica results are presented in figure 3. As can be seen, the loads with replica increases dramatically when the size of the replica victim cache is increased from 1 block to 2 blocks, because the conflicts of replicas in the replica victim cache can be reduced by exploiting the associativity. For the replica victim cache of 4 or more blocks, the loads with replica is larger than 98.6%, which is tremendously larger than the loads with replica achieved by ICR schemes. We use cacti 3.2 model [15] to estimate the area overhead and the results are shown in table 4. As can be seen, the area overhead of the 4-entry replica victim cache is less than 10%, compared to a data cache of 16K, 32K or 64K bytes. Considering both reliability enhancement and hardware overhead, we fix the size of the replica victim cache to be 4 entries.

المنسارة للاستشارات

**Table 4.** The area of a 4-entry fully associative replica victim cache, compared with 4-way associative L1 data caches of 16K, 32K and 64K bytes respectively. The cache block size of both the replica victim cache and the data cache are 32 bytes.

|              | 128B RVC | 16KB D-cache | 32KB D-cache | 64KB D-cache |

|--------------|----------|--------------|--------------|--------------|

| $area(cm^2)$ | 0.001183 | 0.011899     | 0.021325     | 0.038569     |

| ratio        | 100%     | 9.94%        | 5.55%        | 3.07%        |

Fig. 3. Loads with replica for replica victim caches of 1, 2, 4, 8 and 16 blocks.

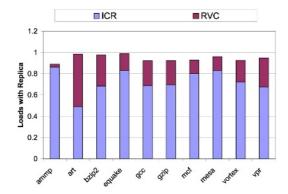

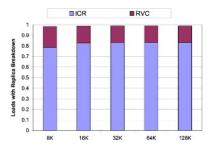

Figure 4 illustrates the loads with replica for a replica victim cache with 4 blocks for all the 10 benchmarks. The replicas can be found either from the L1 data cache (as the ICR approach) or from the replica victim cache. We find that for each benchmark, replica victim cache can store a large portion of the replica victims that are most likely accessed in the future, in addition to the replicas produced by the ICR approach, resulting in significant enhancement on data reliability. The average loads with replica with the replica victim cache is 94.4%, which is 21.7% larger than the ICR approach alone.

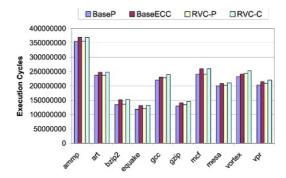

# 5.2 Performance Comparison

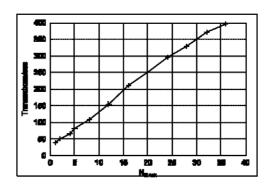

Using the above settings for the replica victim cache, we next study the performance of the replica victim caching. Since the replica victim cache is only used to store the replica victims from the L1 data cache, there is no performance degradation compared to the corresponding ICR approaches [7]. Therefore, we only compare the performance implications of the four schemes described in Section 3.

As shown in figure 5, the performance of the RVC-P scheme is comparable to the BaseP scheme and the performance of the RVC-C scheme is comparable to the BaseECC scheme. Specifically, the average performance degradation of RVC-P to BaseP and RVC-C to BaseECC is 1.8% and 1.7% respectively. It should be noted that this performance degradation comes from ICR, not from the replica victim caching. Since ICR relies on dead block prediction and there is no perfect dead block predictor, some cache blocks in the L1 may be predicted

Fig. 4. Loads with replica for replica victim caches of 4 blocks.

Fig. 5. Performance comparison of different schemes.

dead (and thus are utilized to store replicas) but are actually accessed later (i.e., not "dead" yet), which can result in performance degradation.

# 5.3 Error Injection Results

We conduct the error injection experiment based on random injection model [5]. In this model, an error is injected in a random bit of a random word in the L1 data cache. Such errors are injected at each clock cycle based on a constant probability (called error injection rate in this paper).

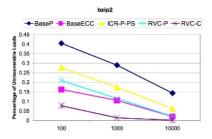

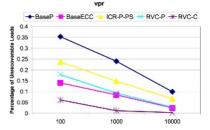

Figure 6 and figure 7 present the fraction of loads that could not be recovered from errors (including single-bit or mult-bit errors) for BaseP, BaseECC, ICR-P-PS, RVC-P and RVC-C for bzip2 and vpr respectively. In both experiments, the data is loaded as a function of the probability of an error occurring in each cycle and the error injection rate varies from 1/100 to 1/1000 and 1/10000. Note that the intention here is to study the data reliability under intense error behavior, thus very high error injection rates are used. As can be seen, BaseP always has the worst error resilient behavior, since the parity bit can only detect

single-bit errors. When the error injection rate is relatively low (i.e., 1/10000), BaseECC has similar percentage of unrecoverable loads as RVC-C. However, as the error injection rate increases, the difference between BaseECC and RVC-C grows larger. Specifically, when the error injection rate is 1/1000, RVC-C can reduce the unrecoverable load by 9.1% and 4.5% for bzip2 and vpr respectively, compared to the BaseECC scheme. Similarly, the RVC-P scheme exhibits much better error resilient behavior compared to BaseP and ICR-P-PS at different error injection rate.

**Fig. 6.** Percentage of unrecoverable loads for bzip2.

**Fig. 7.** Percentage of unrecoverable loads for vpr.

# 5.4 Sensitivity Analysis

To verify the effectiveness of the replica victim cache of 4 blocks for L1 data caches with different configurations, we also make experiments to study the loads with replica by varying the L1 data cache size and the number of associativity. In both experiments, the replica victim cache is fixed to be a fully-associative cache of 4 blocks.

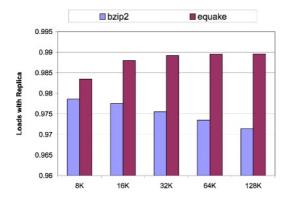

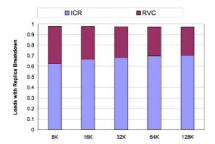

Figure 8 gives the loads with replica for L1 data caches of 8K, 16K, 32K, 64K and 128K bytes. The block size and the associativity of the L1 data cache are 32 bytes and 4 way respectively. The results are very interesting. As can be seen, bzip2 and equake exhibit different trends in loads with replica. As the data cache size increases, the loads with replica of bzip2 decreases slightly, while the loads with replica of equake increases slightly. The reason is that replicas can be found in two places: the L1 data cache and the replica victim cache. The number of replicas that can be stored in the L1 increases as the L1 data cache size increases, however, the relative number of replicas that can be stored in the replica victim cache decreases since the size of replica victim cache is fixed. Therefore, the effect of increasing the L1 data cache size on the loads with replica is dependent on these two factors. The breakdown of loads with replica from the L1 data cache and from the replica victim cache for bzip2 and equake are presented in figure 9 and figure 10 respectively. In figure 9, the decrease of loads with replica from the replica victim cache dominates, and thus the total

loads with replica decreases as the L1 data cache size increases. In contrast, in figure 10, the increase of loads with replica from the L1 data cache dominates, and hence the total loads with replica increases with the increase of the L1 data cache size. However, for all the L1 data cache configurations, the replica victim cache of 4 entries can achieve the loads with replica more than 98.1% on average, which is substantially larger than what the ICR approach alone can achieve.

Fig. 8. Loads with replica for 4-way associative L1 data caches of 8K, 16K, 32K, 64K and 128K bytes. The replica victim cache is fully associative with 4 blocks. The block size of both the L1 data cache and the replica victim cache is 32 bytes. Insensitive to the L1 data cache size, the addition of the fully associative replica victim cache of 4 blocks can achieve the loads with replica more than 98.1% on average.

**Fig. 9.** Loads with replica breakdown for L1 data caches of 8K, 16K, 32K, 64K and 128K for bzip2.

Fig. 10. Loads with replica breakdown for L1 data caches of 8K, 16K, 32K, 64K and 128K for equake.

We also study the loads with replica for L1 data caches with different associativity and find similar results. Therefore, with the addition of a small fully-associative replica victim cache of 4 entries, a very high loads with replica can be achieved to enhance data reliability of ICR further for a variety of L1 data caches.

# 6 Conclusion

This paper studies the limitation of In-Cache Replication and proposes to add a small fully-associative replica victim cache to store the replica victim lines in case of their conflicts with the primary data. We find that with the addition of a small replica victim cache of 4 entries, the loads with replica of the ICR scheme can be increased by 21.7%. On average, 94.4% load hits in L1 can find replicas either in the L1 data cache or in the replica victim cache. We also propose and evaluate two different reliability enhancing schemes — RVC-P and RVC-C — that are proven to be quite useful.

RVC-P is a much better alternative for ICR-P-PS where one may want simple parity protection. It can enhance reliability significantly by providing additional replicas in the replica victim cache without compromising performance. RVC-P also has better performance than RVC-C or ECC based schemes (i.e., BaseECC).

RVC-C can increase the error detection/correction capability by comparing the primary data and the replica before the load returns. Our error injection experiments reveal that RVC-C has the best reliability and can be used for applications that demand very high reliability or operate under highly noisy environments. Compared with the BaseECC scheme, the performance degradation of RVC-C is only 1.7% on average.

In summary, this paper proposes the addition of a small fully-associative replica victim cache to enhance data reliability of ICR schemes significantly without compromising performance. Our future work will concentrate on studying the reliability and performance impact of replica victim cache for multiprogramming workloads. In addition, we plan to investigate how to use a unified victim cache efficiently to store both primary victims and replica victims and the possibility to make a better tradeoff between performance and reliability.

# References

- P. Sweazey. SRAM organization, control, and speed, and their effect on cache memory design. Midcon/87, pages 434-437, Septembe, 1987.

- H. Imai. Essentials of error-control coding techniques. Academic Press, San Diego, CA, 1990.

- 3. C.L. Chen and M.Y Hsiao. Error-correcting codes for semiconductor memory applications: a state of the art review. In Reliable Computer Systems Design and Evaluation, pages 771-786, Digital Press, 2nd edition, 1992.

- 4. J. Karlsson, P. Ledan, P. Dahlgren, and R. Johansson. Using heavy-ion radiation to validate fault handling mechanisms. IEEE Micro, 14(1):8–23. February 1994.

- S. Kim and A. Somani. Area efficient architectures for information integrity checking in cache memories. ISCA, May 1999, pp. 246–256.

- J. Sosnowski. Transient fault tolerance in digital systems. IEEE Micro, 14(1):24

35, February 1994.

- W. Zhang, S. Gurumurthi, M. kandemir and A. Sivasubramaniam. ICR: in-cache replication for enhancing data cache reliability, DSN, 2003.

- 8. S. Kaxiras, Z. Hu, and M. Martonosi. Cache decay: exploiting generational behaviour to reduce cache leakage power, ISCA, June 2001.

- 9. P.Shivakumar, M. Kistler, S. Keckler, D. Burger and L. Alvisi. Modeling the effect of technology trends on soft error rate of combinational logic, DSN, June, 2002.

- N.P. Jouppi. Improving direct-mapped cache performance by the audition of a small fully-associative cache and prefetch buffers, ISCA, 1990.

- 11. M. Hamada and E. Fujiwara. A class of error control codes for byte organized memory system-SbEC-(Sb+S)ED codes. IEEE Trans. on Computers, 46(1):105-110, January 1997.

- 12. S. Park and B. Bose. Burst asymmetric/unidirectional error correcting/detecting codes, FTC, June, 1990.

- Understanding Soft and Firm Errors in Semiconductor Devices. Actel Whitepaper, 2002.

- 14. http://www.simplescalar.com.

- S. Wilton and N. Jouppi. CACTI: An enhanced cache access and cycle time model. IEEE Journal of Solid-State Circuits, Vol. 31(5):677-688, May 1996.

- 16. http://www.spec.org.

# Efficient Victim Mechanism on Sector Cache Organization

Chunrong Lai 1 and Shih-Lien Lu 2

<sup>1</sup> Intel China Research Center, 8F, Raycom Infotech Park A, No.2 Kexueyuan South Road ZhongGuanCun, Haidian District, Beijing China, 100080 chunrong.lai@intel.com

<sup>2</sup> Microprocessor Research, Intel Labs shih-lien.l.lu@intel.com

Abstract. In this paper we present an victim cache design for caches organized with line that contains multiple sectors (sector cache). Sector caches use less memory bits to store tags than non-sectored caches. Victim cache has been proposed to alleviate conflict misses in a lower associative cache design. This paper examines how victim cache can be implemented in a sector cache and proposes a further optimization of the victim buffer design in which only the tags of the victim lines are remembered to re-use data in the sector cache. This design is more efficient because only an additional "OR" operation is needed in the tag checking critical path. We use a full system simulator to generate traces and a cache simulator to compare the miss ratios of different victim cache designs in sector caches. Simulation results show that this proposed design has comparable miss ratios with designs having much more complexity.

# 1 Introduction

In a cache an address tag (or tag) is used to identify the memory unit stored in the cache. The size of this memory unit affects how well a cache functions. For a fixed size cache larger unit size needs less memory bits to store tags and helps programs that possess special locality. However, larger unit may cause fragmentation making the cache less efficient when spatial locally is not there. Moreover, transferring each unit from lower memory hierarchy takes higher bandwidth. Smaller unit size allows more units to be included and may help programs that spread memory usage.

Sector cache[1][2] has been proposed as an alternative to strike a balance of cache unit sizes. A sector cache's memory unit is divided into sub-sections. Each unit needs only one tag thus saves tag memory bits. These sub-sections of a sector cache need not to be simultaneously brought in the cache allowing lower transferring bandwidth. Another advantage of sector caches is observed for multiprocessors systems because they reduce false sharing[3][4]. Sector cache's advantage is evident in that many microprocessors employ sector caches in their designs. For example, Intel's Pen-

tium®  $4^{1}[5]$ , SUN's SPARC<sup>TM</sup>[6] and IBM's POWERPC<sup>TM</sup>  $G4^{TM}[7]/G5^{TM}[8]$  all employ sector cache in their cache organization.

This work intends to propose and evaluate further optimization techniques to improve performance of a sector cache. One of those designs is the victim cache[9]. A victim cache includes an additional victim buffer. When a line is replaced it is put into this small buffer which is full associative instead of just being discarded. The idea is to share the victim buffer entries among all sets since only a few of them are hotly contended usually. First, we discuss how victim buffer/cache idea can be applied in a sector cache. We evaluate two implementations of victim cache. One is called "line-victim" and the other is "sector-victim". We further propose a third victim mechanism design named "victim sector tag buffer"(VST buffer) for further utilize the sector cache lines. This design tries to address a sector cache's potential disadvantage of having larger unit size and could be under-utilized.

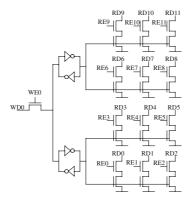

Since there are many different names[3][6][10][11][12][13][14][15] used to describe the units used in a sector cache, we first describe the terminology used in this paper. In our terminology a cache consist of lines which have tags associated with each of them. Each line consists of sub-units which are called sectors. This naming convention is the same as described in the manuals of Pentium® 4[5] and POWERPC<sup>TM</sup>[7][8]. An example 4-way set-associative cache set is shown in figure 1. A valid bit is added to every sector to identify a partial valid cache line. We also use the terminology s-ratio which is defined as the ratio between the line size and the sector size. A sector cache with s-ratio equals to p is called p-sectored cache as [1]. The example in figure 1 it is a 4-sectored cache.

| Address tag |   | Cache data          |

|-------------|---|---------------------|

| А           | ٧ | Sector 0(to A+SL)   |

| Line 1      | ٧ | Sector 1(to A+2*SL) |

| Lille       | V | Sector 2(to A+3*SL) |

|             | ٧ | Sector 3(to A+4*SL) |

| В           | ٧ | Sector 0(to B+SL)   |

| Lina O      | ٧ | Sector 1(to B+2*SL) |

| Line 2      | ٧ | Sector 2(to B+3*SL) |

|             | ٧ | Sector 3(to B+4*SL) |

| Address tag |   | Cache data          |

|-------------|---|---------------------|

| С           | ٧ | Sector 0(to C+SL)   |

| Line 3      | ٧ | Sector 1(to C+2*SL) |

| Line 3      | ٧ | Sector 2(to C+3*SL) |

|             | ٧ | Sector 3(to C+4*SL) |

| D           | ٧ | Sector 0(to D+SL)   |

| Line 4      | ٧ | Sector 1(to D+2*SL) |

| Line 4      | ٧ | Sector 2(to D+3*SL) |

|             | ٧ | Sector 3(to D+4*SL) |

Fig. 1. Principles of sectored cache

This paper is organized as follows. In this section we introduce the concept of sector cache and victim mechanism. In the next section we first review other related works in this area. We then describe in more detail of our design. In section three we present the simulation methodology. In section four and five we introduce our simulation results on different cache levels. Finally we conclude with some observations.

Pentium is a registered trademark of Intel Corp. or its subsidiaries in the United States and other countries.

# 2 Sector Cache with Victim Buffer

#### 2.1 Related Work

Sector caches can be used to reduce bus traffic with only a small increase in miss ratio[15]. Sector cache can benefit in two-level cache systems in which tags of the second level cache are placed at the first level, thus permitting small tag storage to control a large cache. Sector cache also is able to improve single level cache system performance in some cases, particularly if the cache is small, the line size is small or the miss penalty is small. The main drawback, cache space underutilization is also shown in [13].

Rothman propose "sector pool" for cache space underutilization[13]. In the design, each set of set-associative cache compose of totally s-ratio sector lists. Each list has a fix number of sectors that the number is less than the associativity. S-ratio additional pointer bits, associate with a line tag, point to the actual sector as the index of the sector list. Thus a physical sector can be shared in different cache lines to make the cache space more efficient. Unlike our victim mechanism who tries to reduce the cache Miss ratio, this design more focus on cache space reduction. It depends on a high degree set associative cache. The additional pointer bits and the sector lists will make the control more complex. For example, the output of tag comparison need to be used to get the respond pointer bit first then can get the result sector. This lengthens the critical path. Another example is that different replacement algorithms for the cache lines and sector list need to be employed at the same time.

Seznec propose "decoupled sectored cache" [1] [11]. A [N,P] decoupled sectored cache means that in this P-sectored cache there exists a number N such that for any cache sector, the address tag associated with it is dynamically chosen among N possible address tags. Thus a log2N bits tag, known as the selection tag, is associated with each cache sector in order to allow it to retrieve its address tag. This design increases the cache performance by allow N memory lines share a cache line if they use different sectors that some of the sectors have to be invalid at normal sector cache design. Our concern about this design is that the additional tag storage, say N-1 address tags and s-ratio \* log2N selection tags for each line, need large amount of extra storage. Seznec himself use large(32 or 64) s-raio, which will make the validity check and coherence control very complex, to reduce tag storage before decoupling. We tried to implement this idea and saw the line-fill-in and line-replacement policy is important for the performance. If with a line-based-LRU-like fill-in/replacement policy proposed by ourselves, since Seznec did not give enough details of his policies, the decoupled sector cache will not perform better than our VST design, if with similar extra storage, given s-ratio range of 2~8. And, an additional compare need to be performed to the retrieved selection tag to ensure the sector data is right corresponded to the address tag which causes the tag matching. This also lengthens the tag checking critical path.

Victim caching was proposed by Jouppi[9] as an approach to reduce the cache Miss ratio in a low associative cache. This approach augments the main cache with a small fully-associate victim cache that stores cache blocks evicted from the main

cache as a result of replacements. Victim cache is effective. Depending on the program, a four-entry victim cache might remove one quarter of the misses in a 4-KB direct-mapped data cache. Recently [16] shows that victim cache is the most power/energy efficient design among the general cache misses reduction mechanisms. Thus it becomes a more attractive design because of the increasing demand of low power micro-architecture.

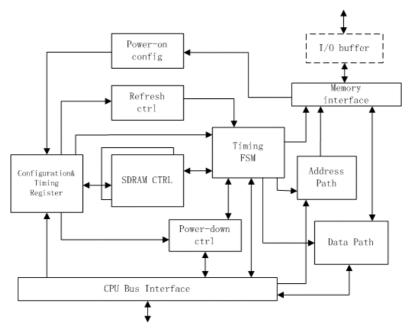

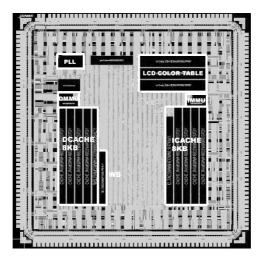

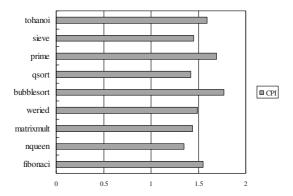

# 2.2 Proposed Design

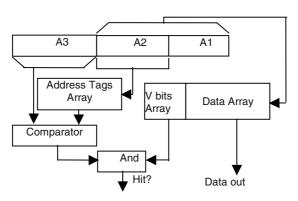

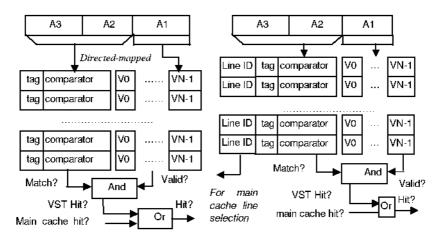

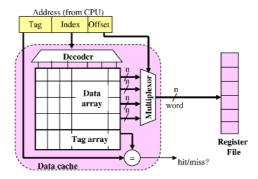

In order to make our description clearer, we define several terms here. We call a reference to a sector cache a block-miss if the reference finds no matching tag within the selected set. We call a reference a data-miss if the tag matches but the referenced word is in an invalid sector. Thus a miss can be either block-miss or data-miss. Similar to [1][11] describe, for a P-sectored cache we divide the address A of a memory block in four sub-strings (A3, A2, A1, A0) defined as: A0 is a log2SL bit string which SL is the sector length, A1 is a log2P bit string show which sector this block is in if it is in a cache line, A2 is a log2nS bit string which nS is the number of the cache sets, A3 consists of the remaining highest significant bits. The main cache line need store only the bits in A3. Figure 2 show tag checking of directed-mapped case. A2 identify the only position of the tag to be compared in the tag array. (A2, A1) identify the only position the data sector can be. The data can be fetched without any dependency on the tag comparison. The processor pipeline may even start consuming the data speculatively without waiting for the tag comparison result, only roll back and restart with the correct data in the case of cache miss which is rarely happened, as line prediction.

Fig. 2. Directed mapped sector cache tag checking

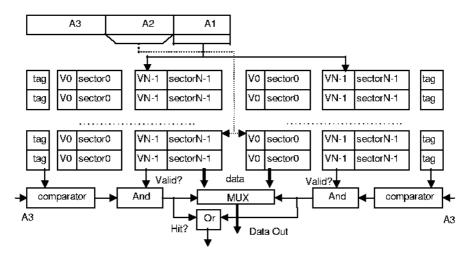

In the case of set-associative cache, (A2, A1) can only select the conceptual "sector set", then waiting for the comparison result of the address tags to get a line ID to deliver the correspond sector. Figure 3 is such an example of a 2-way associate sector

cache. In a lower-associate cache the sector data and the valid bits being select can be got independently with the tag comparison.

Fig. 3. 2-way associate sector cache tag checking

In figure 3 a line ID is needed, in critical path, as selection signal of the MUX. Line ID is founded after the tag comparison result. For a higher associate cache like a CAM, where a simple MUX may not be used, the data and valid bits could be not right at hand immediately. But Line ID retrieving still dominates in the critical path there[17].

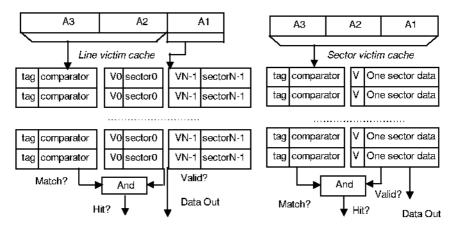

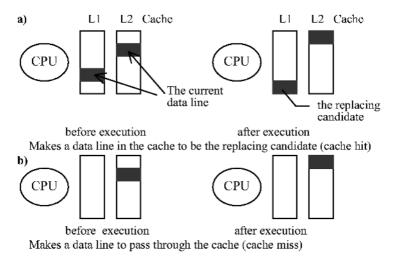

As mentioned by many researchers victim cache can reduce cache Miss ratio. There are two straightforward victim designs for sector cache. One is line-victim cache(LVC), the other is sector-victim cache(SVC). Figure 4 show their tag checking. Tag checking of the line victim cache is in the left and the other is in the right. The most difference between them is the data unit associate with the victim tag. In line-victim cache, the data unit is a cache line. And the data unit is a sector in the sector-victim cache. Thus the lengths of the victim tags of LVC and SVC are different. For same entries number LVC can be expected more cache misses saved due to more storage there, where SVC can be expected a little faster tag checking and data retrieve. Figure 4 do not connect the victim cache with main cache to avoid unnecessary complexity and allow architects to decide if swap the victim data with the main cache data when hit victim cache.

Both line-victim cache and sector-victim cache are paralleled accessed with the main sector cache. A cache line is evicted to the line- victim cache in case of cache replacement happens. As to the sector-victim cache, only the valid sectors in the whole line are evicted to the sector-victim-cache. Also when a new line is brought into cache, the sector-victim cache is checked to see if there are other sectors in the same line. If so the victim sectors are also brought into the main cache line to main-

tain a unique position of a cache line.

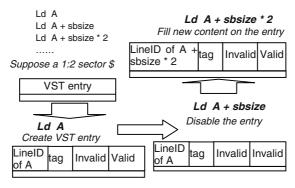

We know some of the requested data may still be in the data cache but it is just inaccessible because it has been invalidated. This paper describes another approach, called "VST buffer" to remember what is still in the data cache.

Fig. 4. Tag checking of line-victim cache and sector-victim cache

When a block miss happens and the set is full, a cache line must be replaced. Each sector of the replaced line will be mark as invalid. A new sector will be brought into the replaced line, and the cache tag will be updated. Thus some of the previously replaced line's sector data may still be in the data array since not all sector, of the newly brought in cache line, is brought in. Only their valid bits are marked invalid. VST buffer is used to keep track of these sectors whose data is still the data array. Thus a VST entry consists of the victim tag, the victim valid bits and the "real location" line ID in the cache set. For a directed mapped main cache the line ID field is needless. The left side of figure 5 shows the VST buffer tag checking with a directed-mapped main cache. As seen from the figure the VST buffer produce an additional "VST hit" signal to be perform "or" operation with the main cache hit signal in the critical path, without affecting the sector fetching and consuming. In either a VST hit or a main cache hit the data can be processed continuously.

The right side of figure 5 shows the VST buffer tag checking of a set-associate main cache. A VST hit not only leads to a hit result but also deliver a line ID to the main cache selector to get the result data. This line ID signal is performed "or" operation with the main cache line ID signal to select final line. One extra cost here is when a new sector is brought into the main cache, if a data miss happens, the VST needs to be checked if the position contains a sector being victimized. If so the victim entry is invalidated or thrashed. This does not increase cache-hit latency since it happens when cache miss. Since there is already cache miss penalty the additional cost seems to be acceptable.

When compare the cost of the three victim mechanism connected with a p-Sectored Cache all compose of N entries. We see beside the similar comparators and the control, the line- victim cache need N line tags, data of N \* line size and N\*P

Fig. 5. Tag checking of Victim Sector Tag Buffer (VST buffer) with sector cache

valid bits; the sector-victim cache need N sector tags (each of it is log2P bits longer than a line tag), data of N \* sector size and N valid bits; and the VST buffer need N line tags, N \* P valid bits and N \* log2Assoc bits of line IDs which Assoc is the cache associativity. So the line victim cache needs most resource among them as VST buffer need least resource.

In MP system, where the sector cache is proved efficient, there need additional cache coherence protocol, like MESI, to maintain the cache coherence. We think the victim mechanism will make the MP sector cache coherence protocol more complex. But we will not discuss the details here since it is beyond this paper's scope.

# 3 Simulation Methodology

Several SpecCPU2K[18] benchmarks (compiled with compiler option "-O3 -Qipo"), Java workload SpecJBB2K[19] with Java runtime environment JSEV1.4.1 which is an integer benchmark, and two commercial-like floating-point benchmarks, one is a speech recognition engine[20], the other is an echo cancellation algorithm[21] in audio signal processing, are used in our study.

In order to consider all the effects, including system calls, we use a full system simulator to generate memory reference traces. The simulator used is called SoftSDV[22]. The host system runs Windows 2000 and the simulated system is WindowsNT in batch mode using solid input captured in files. Then we run the traces through a trace-driven cache simulator.

We generate both L1 memory reference traces and L2 memory reference traces. After 20 billion instructions after system start up (the target application is configured auto-run in the simulation) we collect 200 million memory references as our L1 traces. We use 100 million references of them to warm up L1 cache and analysis the behavior of the latter 100 million. The L1 sector cache we simulated is mainly configured as below with small varieties: 16KBsize, 64B line size, 16B sector size, 4 way associ-

ate, LRU replacement algorithm and write-back approach. For L2 cache behavior we use a built-in first level cache together with trace generation. We warm up the built-in cache with 1 billion instructions. Then we collect L2 traces consist of 200 million read references. Also in our simulation we use 50 million L2 references to warm up the L2 cache. The hierarchy consist L2 sector cache we simulated is mainly configured as below with small varieties: L1: 16KBsize, 32B line size, 4-way associate, LRU replacement algorithm and write-back approach. L2: 1MB size, 128 byte line size, 32 byte sector size, 8-way associate, LRU replacement algorithm and write-back approach.

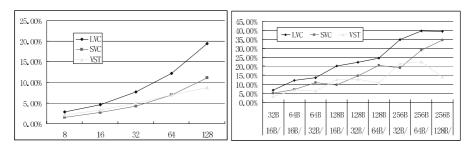

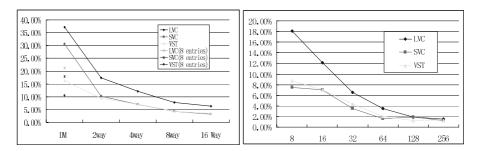

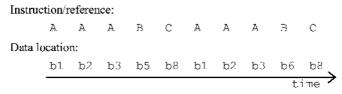

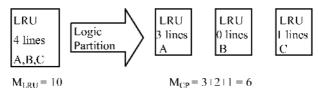

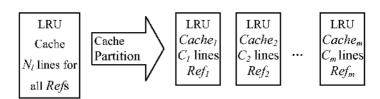

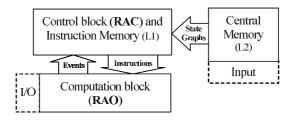

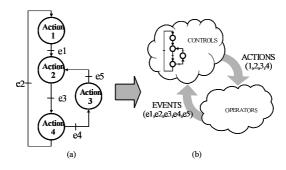

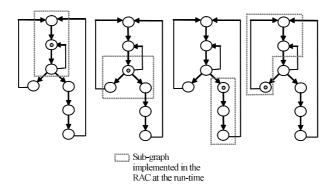

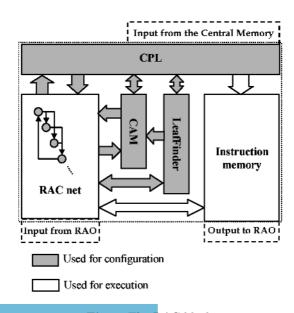

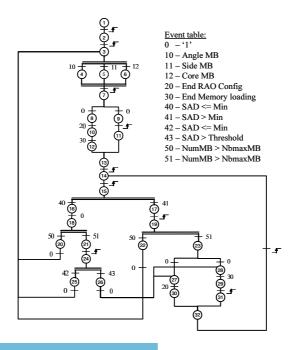

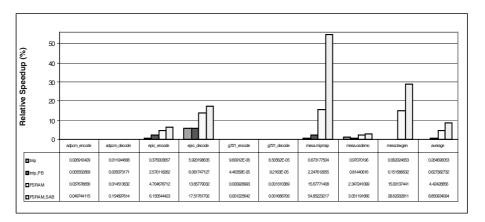

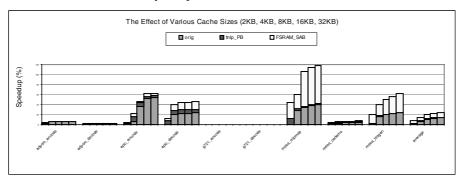

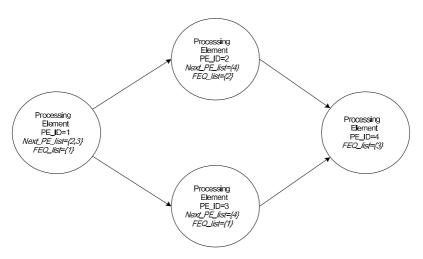

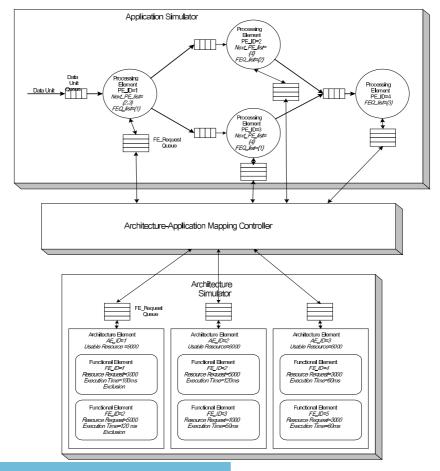

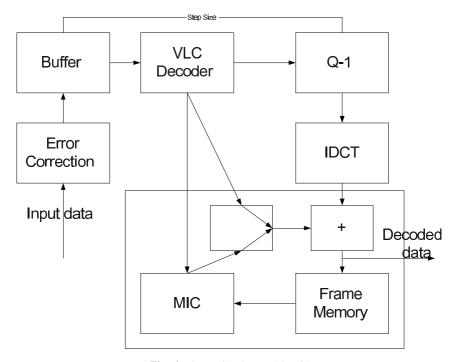

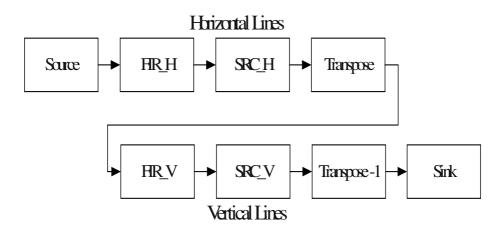

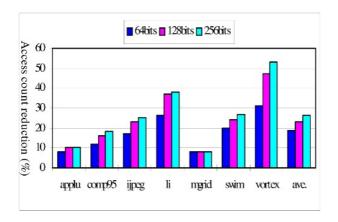

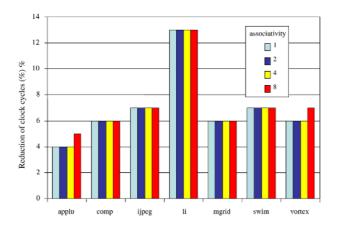

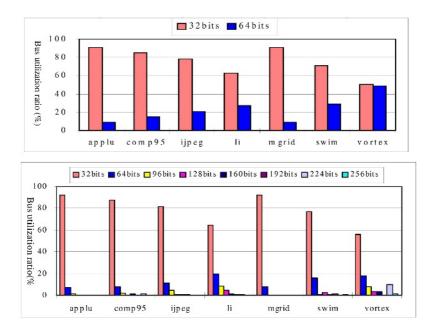

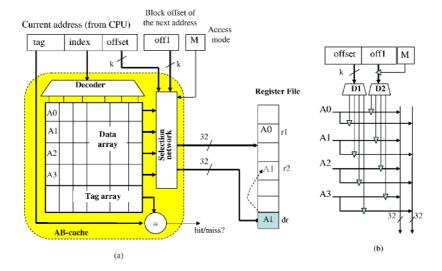

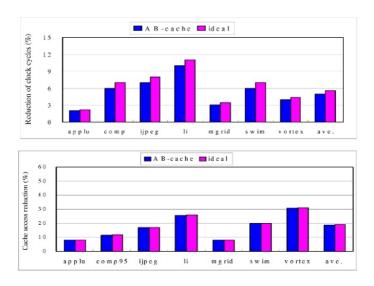

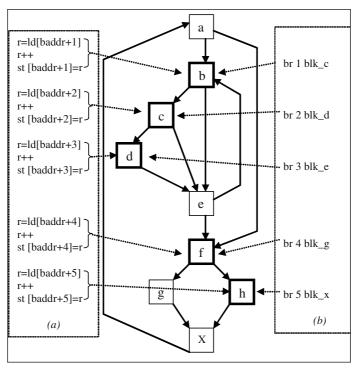

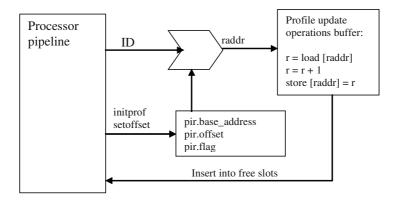

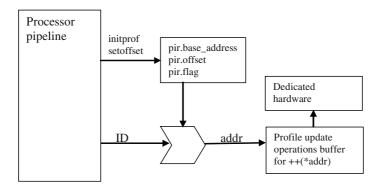

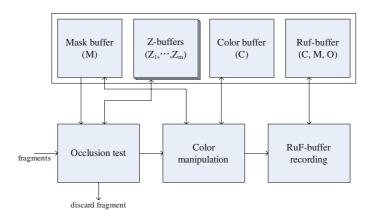

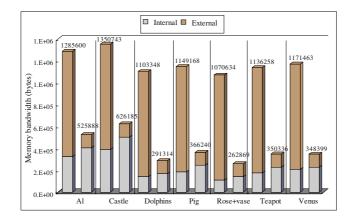

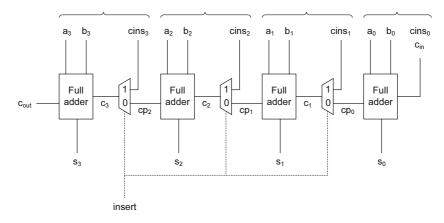

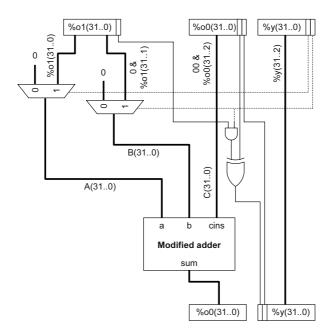

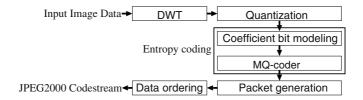

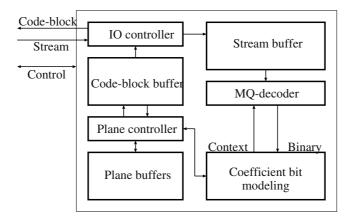

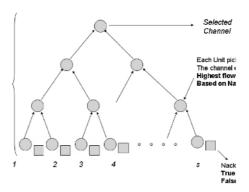

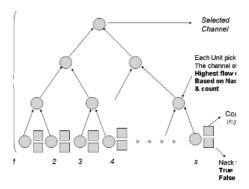

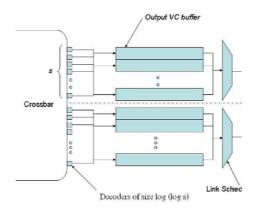

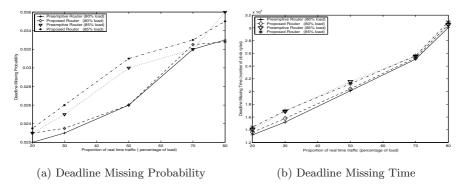

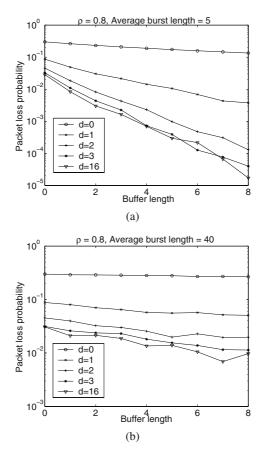

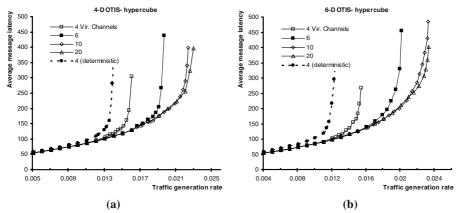

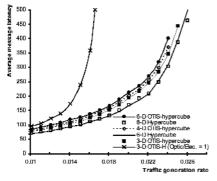

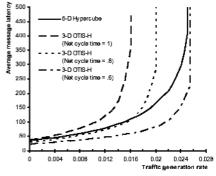

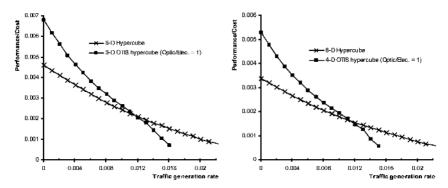

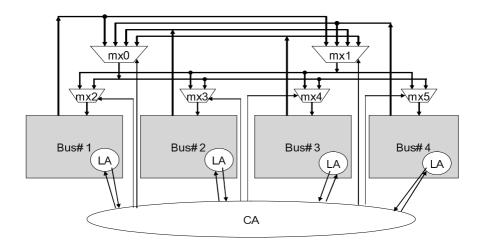

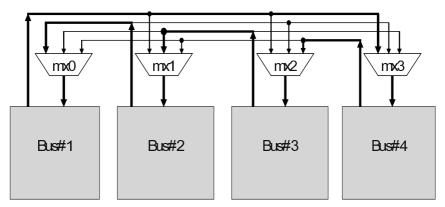

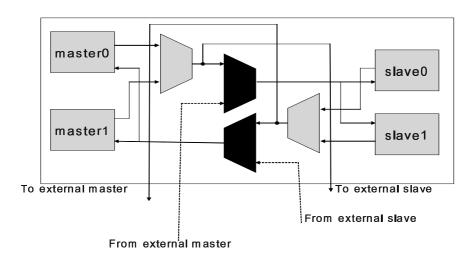

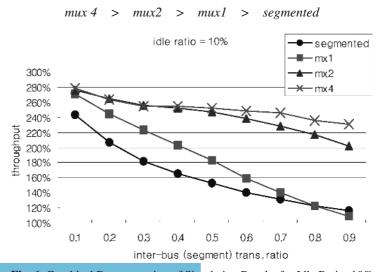

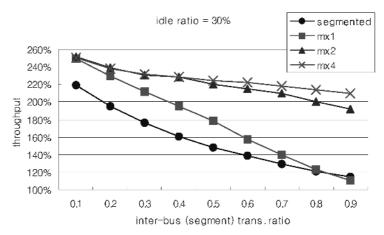

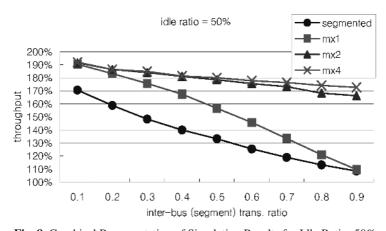

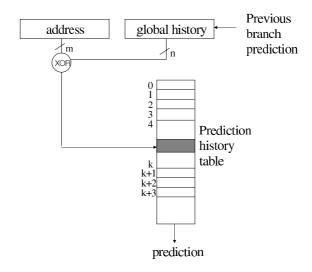

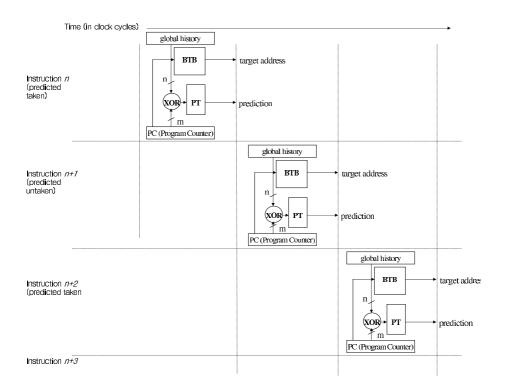

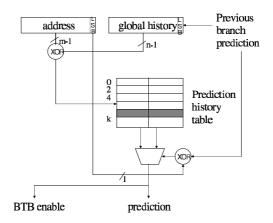

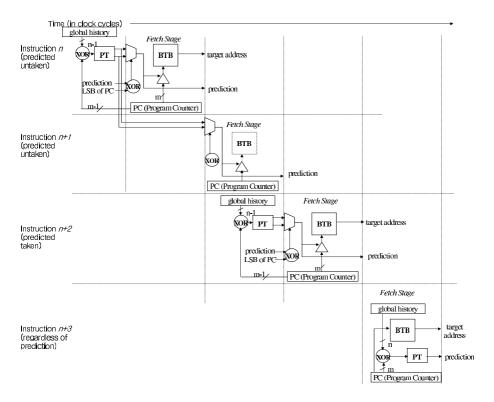

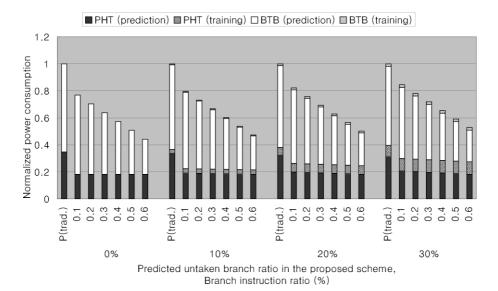

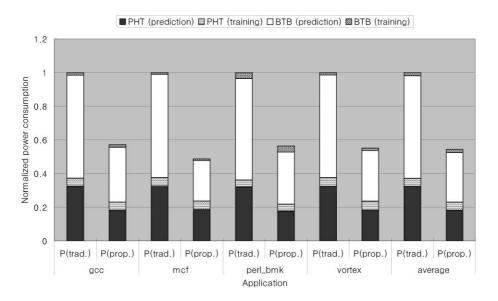

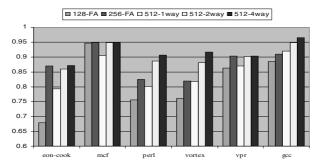

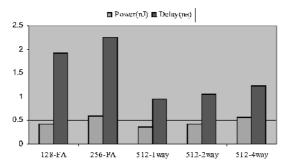

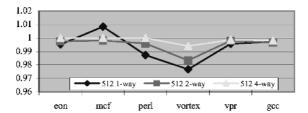

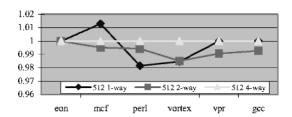

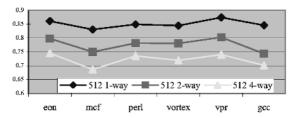

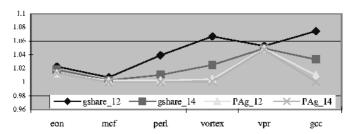

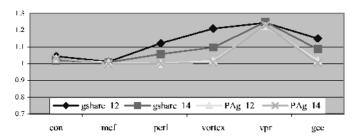

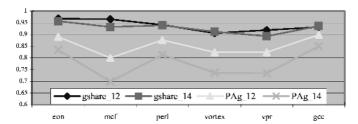

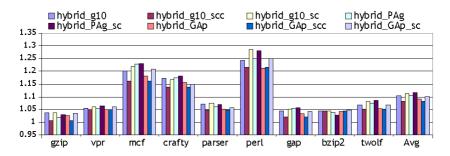

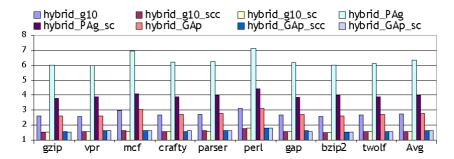

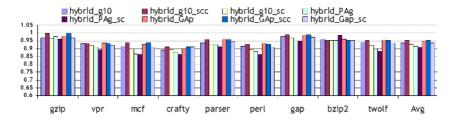

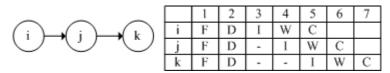

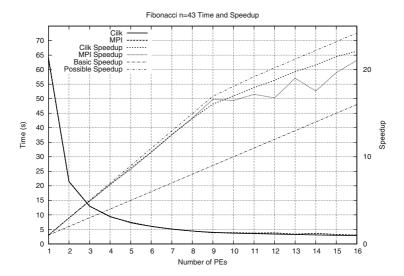

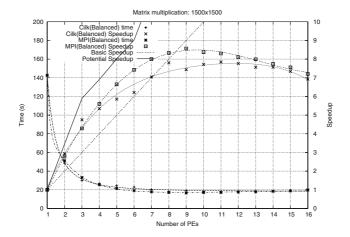

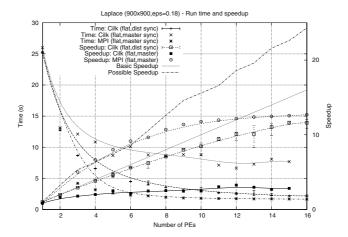

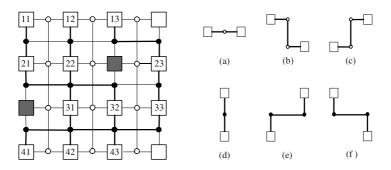

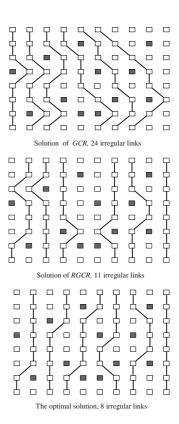

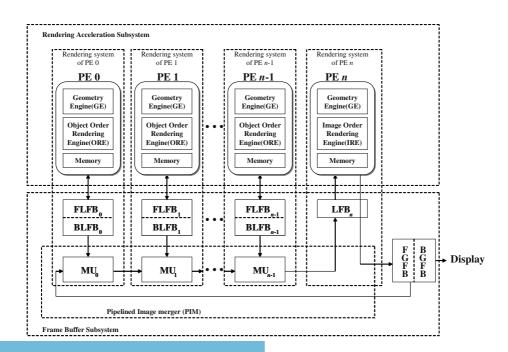

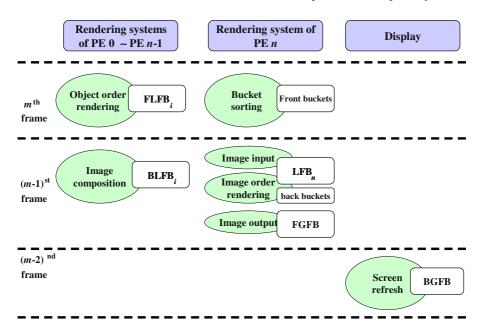

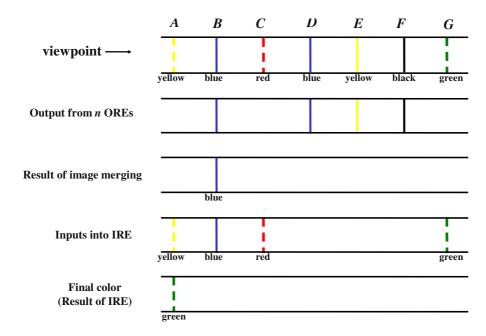

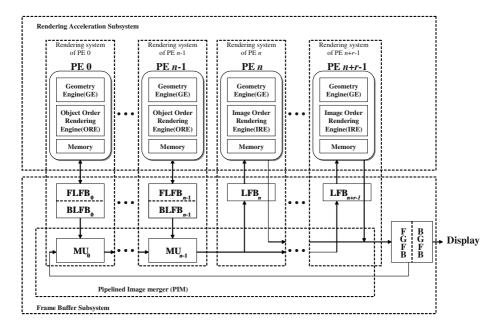

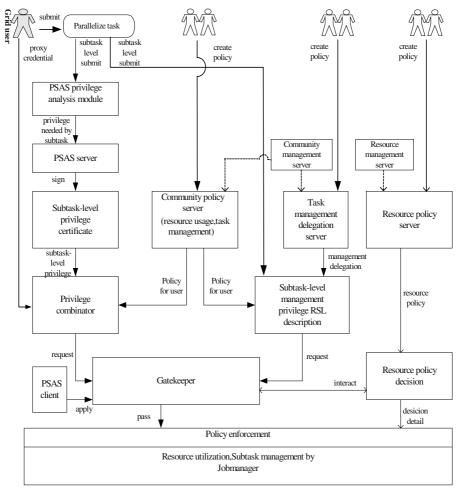

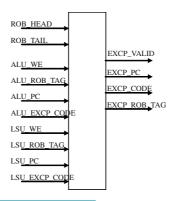

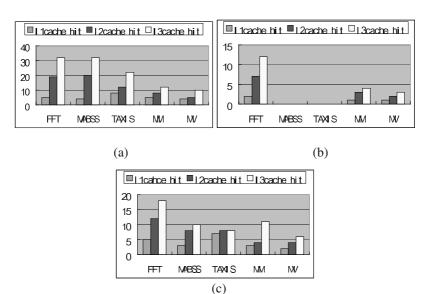

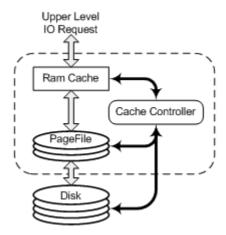

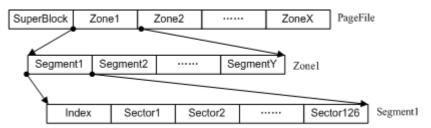

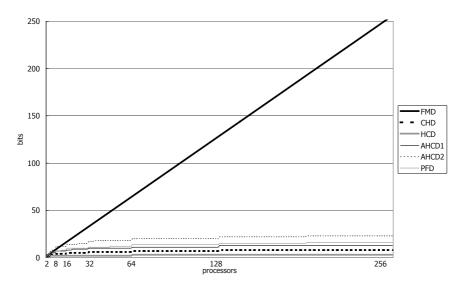

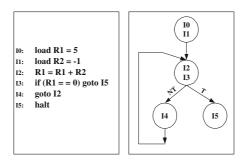

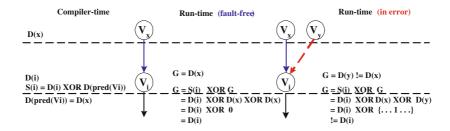

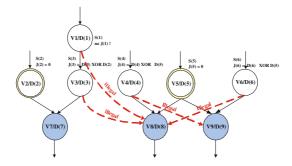

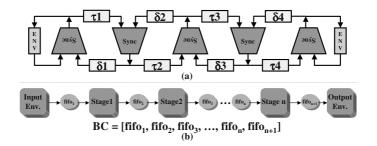

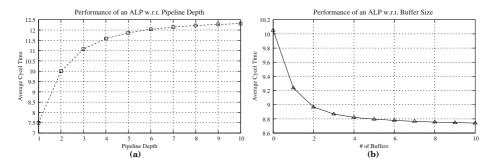

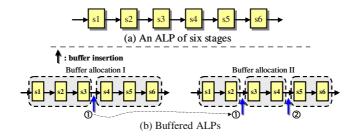

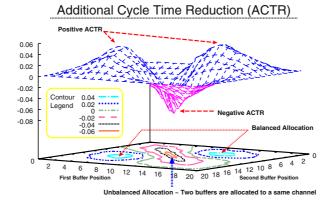

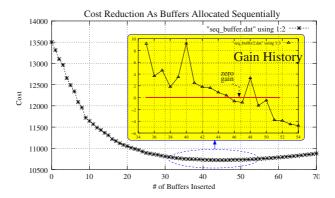

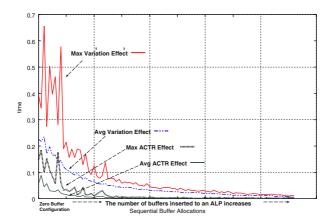

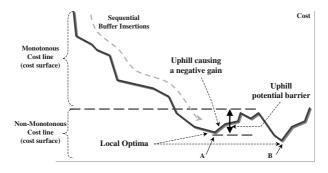

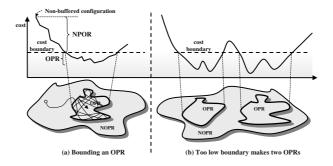

#### 4 Level 1 Sector-Cache Simulation Results and Discussion